# 基于ModelSim的仿真

ModelSim仿真工具是Mentor公司开发的。它支持 Verilog、VHDL以及它们的混合仿真,它可以将整个程序分步执行,使设计者直接看到他的程序下一步要执行的语句,而且在程序执行的任何步骤任何时刻都可以查看任意变量的当前值,可以在Dataflow窗口查看某一单元或模块的输入输出的连续变化等,是目前业界最通用的仿真器之一。

## 基本仿真步骤

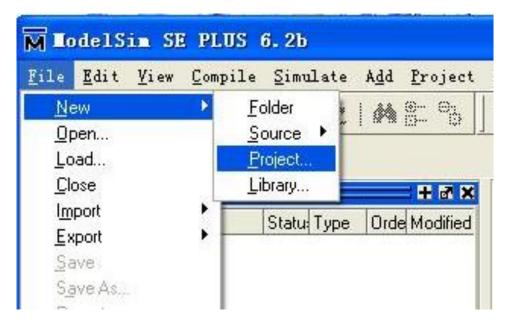

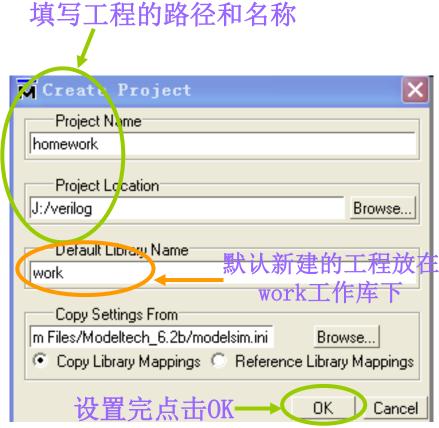

> 建立工程

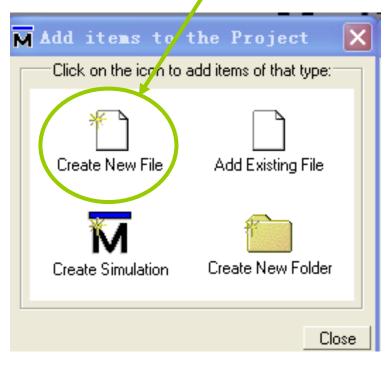

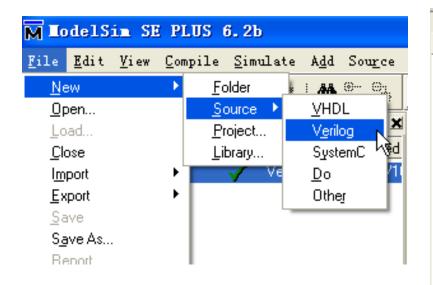

### > 新建文件

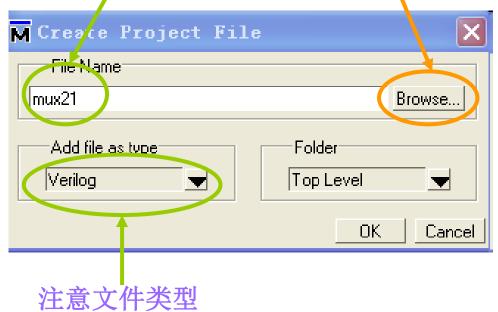

若新建verilog文件,点击此控件

填写文件名,同时可设置文件保存的路径

#### > 编写模块

#### 上述设置完后弹出编写程序窗口,编写程序,保存

```

h]J:/verilog/mux21.v

ln # |

1    module mux_beh(out,a,b,sel);

2    input a,b,sel;

3    output out;

4    assign out=(sel= =0)?a : b;

5    endmodule

6

7

```

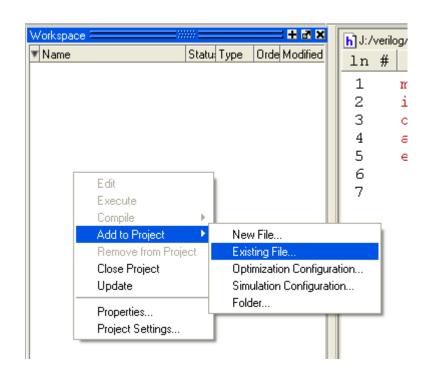

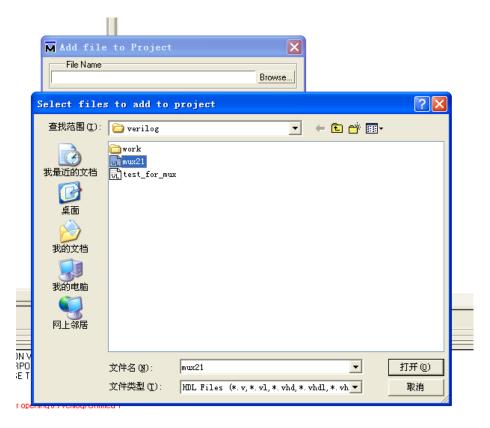

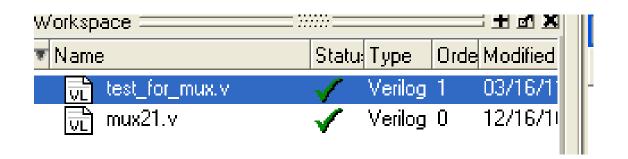

#### 将上述文件加入到新建的Project中

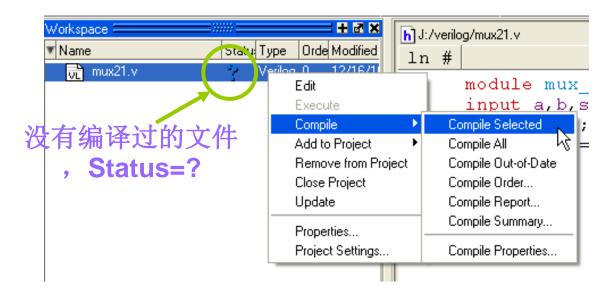

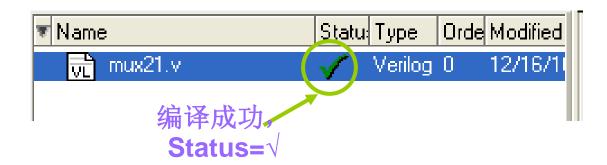

#### ✓ 编译代码

#### ✓ 编写仿真平台

```

h] J:/verilog/test_for_mux.v

ln #

1

module test for mux;

reg a,b,sel;

mux21 mux1(out, a, b, sel);

initial

begin

a=0;b=1;sel=0;

6

#10 a=1;

#10 b=0;

#10 sel=1;

#10 $finish;

10

11

end

12

initial

13

$monitor($time, "a=%b b=%b sel=%b out=%b", a, b, sel, out);

14

endmodule

15

```

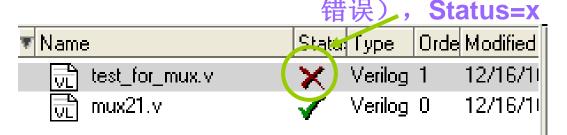

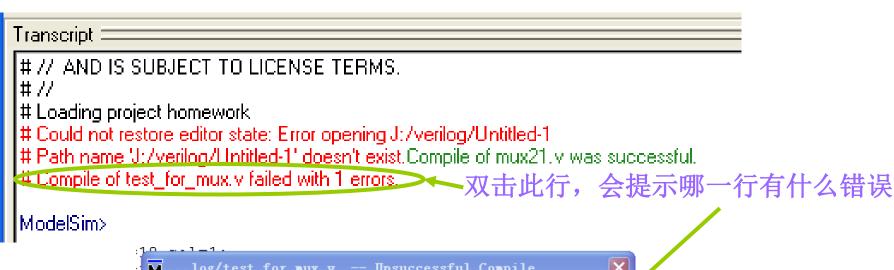

#### ✓ 编译代码

# 编译失败(有语法

✔ 修改文件,保存并重新编译,直到成功为止。

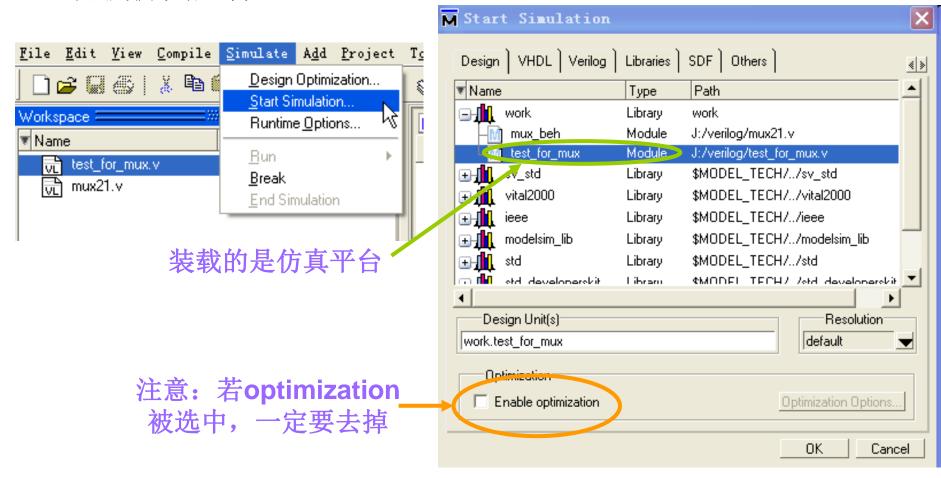

#### ✓ 装载仿真文件

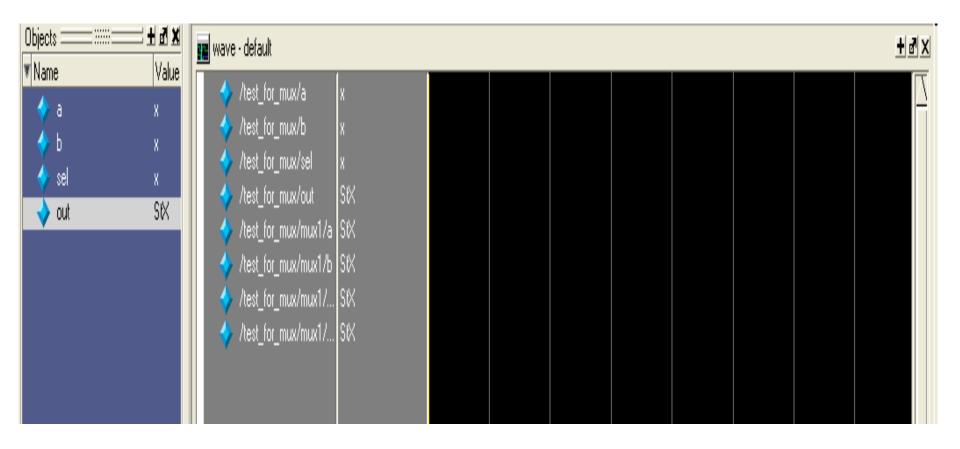

### ✓ 弹出相应窗口,开始仿真

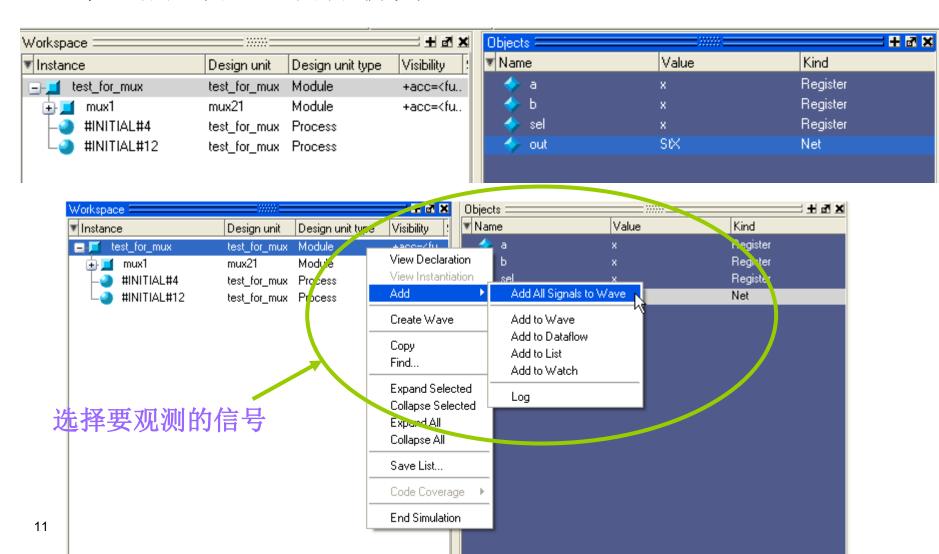

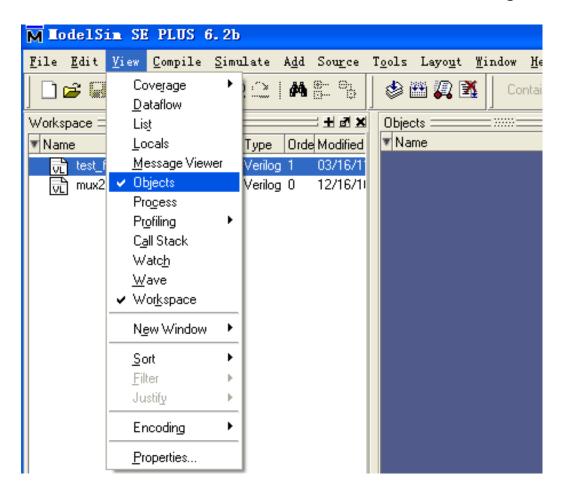

## ✓ 若没有弹出上述窗口,请选择View--Objects

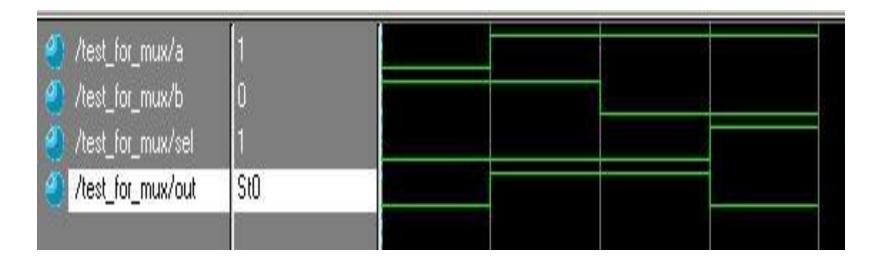

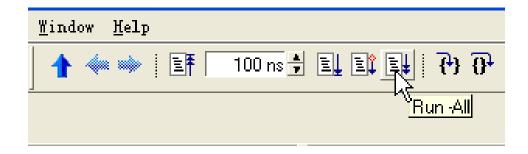

## ✔开始仿真, 查看仿真结果

```

Transcript :

VSIM 7> quit-sim

ModelSim> vsim -novopt work.test_for_mux

# vsim -novopt work.test_for_mux

# Refreshing work.test_for_mux

# Loading work.test_for_mux

# Refreshing work.mux21

# Loading work.mux21

lVSIM 9> ru<del>n-</del>

a=0 b=1 sel=0 out=0

a=1 b=1 sel=0 out=1

a=1 b=0 sel=0 out=1

a=1 b=0 sel=1 out=0

# ** Note: $finish : J:/verilog/test_for_mux.v(10)

Time: 40 ns. Iteration: 0. Instance: /test_for_mux.

|#1

# Break in Module test_for_mux at J:/verilog/test_for_mux.v line 10

VSIM 10>

```

| 测试结果:       |                   |

|-------------|-------------------|

| 系统时刻 寄存器变量值 |                   |

| 0           | a=0 b=1 s=0 out=0 |

| 10          | a=1 b=1 s=0 out=1 |

| 20          | a=1 b=0 s=0 out=1 |

| 30          | a=1 b=0 s=1 out=0 |