# 11.3 PCB的EMC设计

在高速电路中,其中的IC封装等问题是影响EMC性能的重要因素之一。新的封装设计需要减少IC的寄生参数,进而削弱寄生效应。IC的寄生效应包括噪声、延迟、边沿速率、频率响应、天线效应等。

随着技术的发展,IC设计、IC封装及PCB设计间的关系越来越密切。IC设计的总体布局不仅受到工艺的限制,同时也要兼顾PCB板级的许多制约因素。

### PCB的EMC设计技术

- 集成电路 (IC) 封装技术

- 新的封装设计在于减小IC的寄生参数,进 而消弱寄生效应。

- PCB设计技术

- EMC预测技术与EDA技术

- 时钟展频技术

- 过孔设计技术

- ESD防护技术

- 消弱高速电路中的噪声效应。

### PCB电磁兼容性设计的一般原则

#### PCB板层布局原则

- ■确定合适的PCB尺寸。

- ■对高速高性能系统在目标允许的情况下采用叠层设计。

- 关键电源平面与其对应的地平面相邻。

- 参考面的选择应优选地平面。

- 相邻层的关键信号不跨分割区。

- 元件面下面有相对完整的地平面。

- 合理布局各种信号线。

- 高频、高速、时钟等关键信号有一相邻地平面。

- 在高速电路设计中,避免电源平面层向自由空间辐射能量。

#### 地线、电源线和信号线布置原则

#### 1. 地线的布置

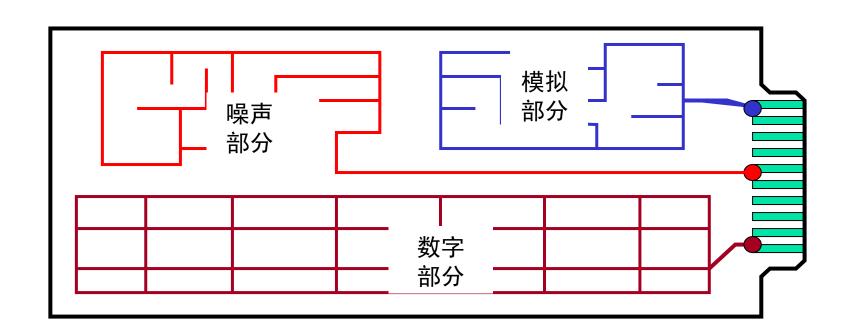

在电路设计中,地有多种含义,比如"数字地"、"模拟地"、"信号地"、"噪声地"、"电源地"等。处理接地问题应注意以下问题:

- •在小信号与大电流电路做在一起的电路中, 必须将地(GND)明显地区分开来。

- •正确选择单点接地与多点接地。

- •数字地与模拟地分开。

- •接地线应尽量加粗。

- •接地线构成闭环路。

## 线路板上的地线示意图

#### 2. 电源线的布置

供电环路面积应减小到最低程度,不同电源的供电环路不要相互重叠。印制电路板上的供电线路应加上滤波器和去耦电容。

#### 3. 信号线的布置

- •不相容的信号线应相互隔离。

- •尽量减小信号环路的面积。

- •考虑阻抗匹配问题。

- •输入、输出线在连接器端口处应加高频去耦电容。

- •尽量缩短模块间印制电路板的外接电缆。

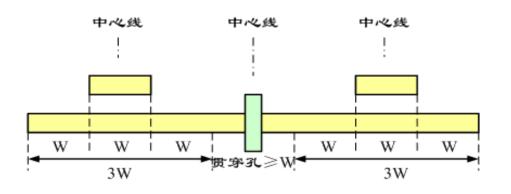

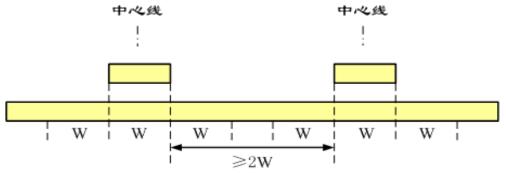

#### 布线设计原则

PCB走线中应遵循3W法则。所有走线的分割距离满足: 走线边沿间的距离应大于或等于2倍的走线宽度,即中心 线之间的距离为走线宽度(W)的3倍。

在涉及PCB的设计中,相关的电磁兼容性研究随着技术的不断进步、工艺的不断改进、复杂度的不断提高,也需要在实际进一研究中不断发展。