# Reduced Instruction Set computers

**Computer Organization and Architecture**

SOUTH CHINA UNIVERSITY OF TECHNOLOGY

FALL 2016

DR. MAO Aihua ahmao@scut.edu.cn

### **Background: Major Advances**

- The Family Concept

- Separate architecture from

- o IBM System/360 1964

- O DEC PDP-8

- Microprogrammed Control Unit (cf CH 17)

-----

- Ease the design for control unit

- Suggested by Wilkes 1951

- Produced by IBM S/360 1964

- Cache Memory

- □ IBM S/360 model 85 1969

### **Major Advances in Computers(2)**

- **Pipelining**

- Introduces parallelism into fetch execute cycle

- Multiple processors

- Reduced Instruction Set Computer (RISC) architecture

- Dramatic departure from the historical processor architecture

3

### **Driving force for CISC**

- CISC-Complex Instruction Set Computer

- Why CISC?

- Software costs far exceed hardware costs

- Increasingly complex high level languages (HLL): structured programming or object-oriented design, allow algorithms more concisely

- Semantic gap: Difference between operations provided in HLLs, lead to complier complexity

### **Driving force for CISC**

- To close the gap, Leads to:

- Large instruction sets

- More addressing modes

- Hardware implementations of HLL statements

- ▼e.g. CASE (switch) on VAX

5

### **Intention of CISC**

- Ease compiler writer

- Improve execution efficiency, because complex operations can be implemented in microcode

- Support more complex HLLs

A different approach of the studies results is to make the architecture that supports the HLL simpler rather more complex- RISC

## Why CISC?

- Smaller programs?

- Program takes up less memory

But memory is now cheap

• Fewer instructions to be fetched, reducing page faults.

Occupy more bits in symbolic machine language

- More instructions in CISC require longer op-codes

- RISC tend to emphasize register, and register references require fewer bits

7

### Why CISC?

- Faster programs?

- More complex control unit

- Microprogram control store larger

- o thus simple instructions take longer to execute

- It is far from clear that CISC is the appropriate solution

### The Next Step - RISC

- RISC-Reduced Instruction Set Computer

- Key features

- Large number of general purpose registers, or use of compiler technology to optimize register use

- Limited and simple instruction set

- Emphasis on optimising the instruction pipeline

9

### **Key Points**

more predictable operations.

A RISC Instruction Set architecture leads itself to the <u>delayed branch technique</u> (instruction are rearranged to occur later so to improve pipeline efficiency).

### **Execution Characteristics of RISC**

- The development of RISC was based on the study of instruction execution characteristics

- Operations performed

- determine functions to be performed and interactions with memory

- Operands used (types and frequencies)

- \*determine memory organization and addressing modes

- Execution sequencing (Procedure calls)

- \* determines the control and pipeline organization

13

### **Execution Characteristics**

------

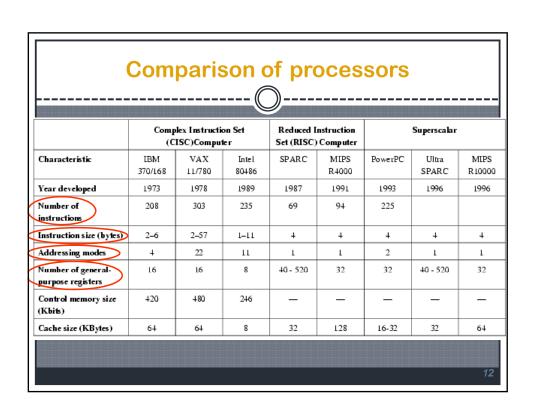

- The following table summarizes the results of a number of studies of high-level-language programs.

All of the results are based on dynamic measurements.

- Vocabulary

- O Dynamic studies are measured during the execution of the program.

- Static measurements merely perform these counts on the source text of a program.

| Relative Dynamic Frequency  |        |                       |     |                                     |     |                           |     |  |  |

|-----------------------------|--------|-----------------------|-----|-------------------------------------|-----|---------------------------|-----|--|--|

| Relative<br>frequency of    |        | Dynamic<br>Occurrence |     | Machine-<br>Instruction<br>Weighted |     | Memory-Reference Weighted |     |  |  |

| occurrence of               |        | Pascal                | С   | Pascal                              | С   | Pascal                    | С   |  |  |

| various HLL instructions in | ASSIGN | 45%                   | 38% | 13%                                 | 13% | 14%                       | 15% |  |  |

| different<br>programs       | LOOP   | 5%                    | 3%  | 42%                                 | 32% | 33%                       | 26% |  |  |

|                             | CALL   | 15%                   | 12% | 31%                                 | 33% | 44%                       | 45% |  |  |

|                             | IF     | 29%                   | 43% | 11%                                 | 21% | 7%                        | 13% |  |  |

|                             | GOTO   | _                     | 3%  | -                                   | _   | -                         | -   |  |  |

|                             | OTHER  | 6%                    | 1%  | 3%                                  | 1%  | 2%                        | 1%  |  |  |

|                             |        |                       |     |                                     |     |                           | 15  |  |  |

### **Operations**

- The results from the table suggest that:

- Assignment statements predominate, movement of data is of high importance

- Preponderance of Conditional statements (IF, LOOP)

- The results are representative for the CISC

### **Operands**

- The dynamic frequency of occurrence of classes of variables

- Majority are local scalar (non-composite) variables

- Optimization is the mechanism for storing and accessing local

|                     | Pascal | С   | Average |

|---------------------|--------|-----|---------|

| Integer<br>Constant | 16%    | 23% | 20%     |

| Scalar Variable     | 58%    | 53% | 55%     |

| Array/Structure     | 26%    | 24% | 25%     |

**Procedure Calls**

- Two aspects are significant:

- The number of parameters and variables that a procedure deals with

- The level of nesting

- Most procedures were passed fewer than 6 arguments and used fewer than 6 local scalar variables

- A high proportion of operand references is to local

### **Implications**

- Making instruction set architecture close to all HLL is not most effective design strategy (only a few used most)

- Best support is to optimize the most used and most time consuming features of typical HLL programs

- From the work of a number of researchers, three elements characterize RISC architectures.

19

### **Implications**

- Operand referencing optimization coupled with locality of references ⇒ memory references reduced

- 2. Careful design of instruction pipelines

- o Conditional branch and procedure call

- Simplified (reduced) instruction set is indicated

### Use of a Large Register File

- From the analysis

- Co Large number of assignment statements in HLL program, A←B

- Most accesses to local scalars

- Heavy reliance on register storage is suggested

- Minimizing memory access

- allows the most frequently accessed operands to be kept in registers and minimizes the register-memory operations

21

### **Registers for Local Variables**

------

- Store local scalar variables in registers

- Reduces memory access

- Some problems

- Every procedure call changes locality

- On every call, local variables must be saved to memory so the register can be reused

- On return, the local variables from the calling program must be loaded back to the register, so the variables from calling programs are restored.

### **RISC Characteristics**

- Register to register operations

- Simple addressing modes

- Simple instruction formats

23

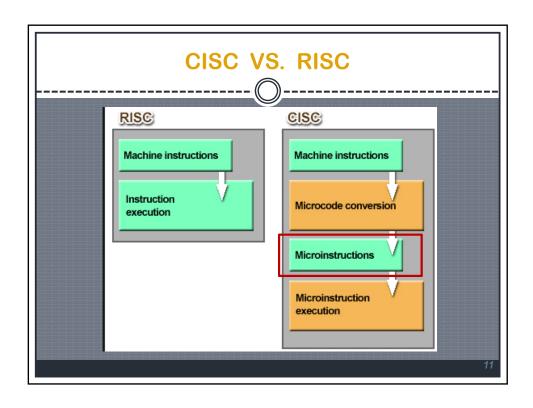

### **One Instruction Per Machine Cycle**

-----

- ofetch two operands from registers

- operform an ALU operation

- store the result in a register

- With one-cycle instructions, there is little or no need for microinsruction

- Machine instructions can be hardwired

### **Register-to-Register Operations**

- Most operations is register-to-register

- Only LOAD and STORE accessing memory

- Simplify instruction set and control unit

- RISC include only 1 or 2 ADD instructions

- While VAX has 25 different ADD instructions

- Encourages the optimization of register use

- Frequently accessed operands remain in high-speed storage

25

### **Simple Addressing Modes**

------

- Almost all RISC instructions use simple register addressing

- May include several additional modes

- Displacement and PC-relative

- Simplify instruction set and control unit

### **Simple Instruction Formats**

- Instruction length is fixed and aligned on word boundaries

- Field locations, especially the opcode, are fixed

- Opcode decoding and register operand accessing can occur simultaneously

- Simplify control unit

27

### Typical of a RISC

- A single instruction size (typically 4 bytes)

- A small number of data addressing modes (typically less than five)

- No indirect addressing

- No operations that combine load/store with arithmetic

- Add from memory

- No more than one memory-addressed operand per instruction

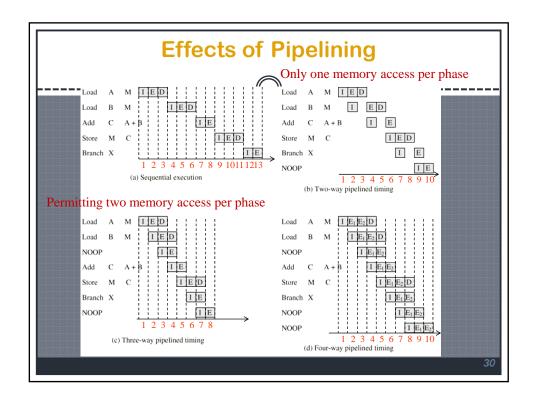

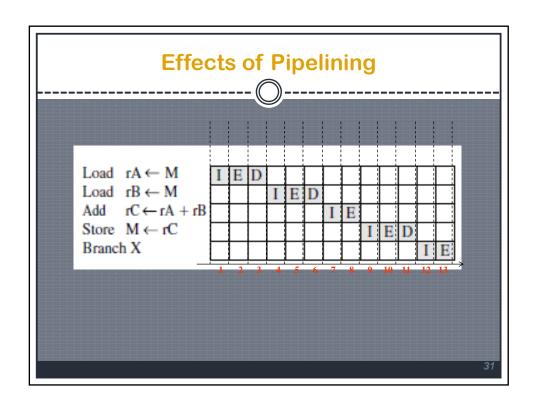

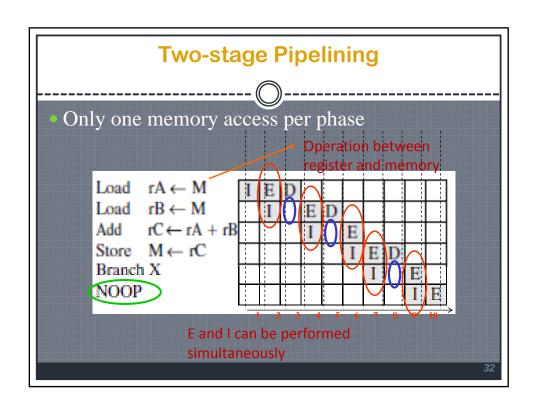

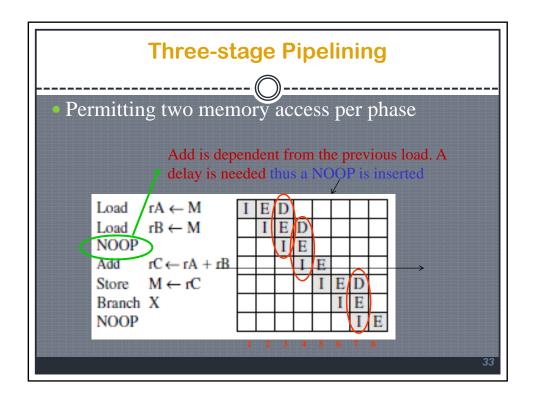

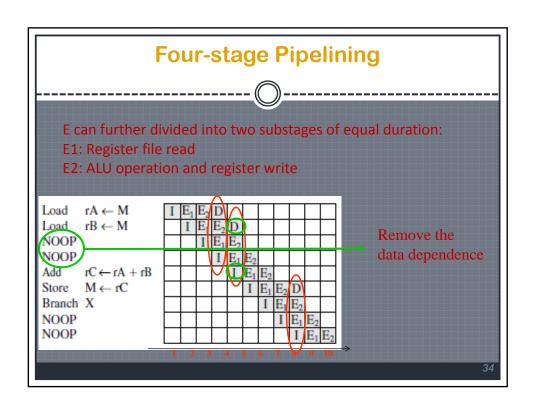

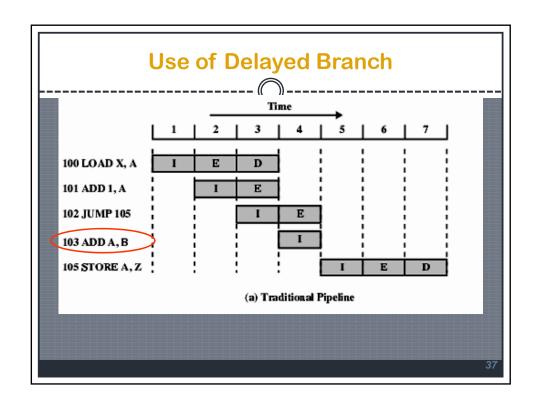

### **RISC Pipelining**

- RISC: Most instructions are register to register

- Two phases of execution

- ol: Instruction fetch

- E: Execute (ALU operation with register input and output)

- For load and store: three stages

- I: Instruction fetch

- E: Execute (Calculate memory address)

- D: Memory (Register to memory or memory to register operation)

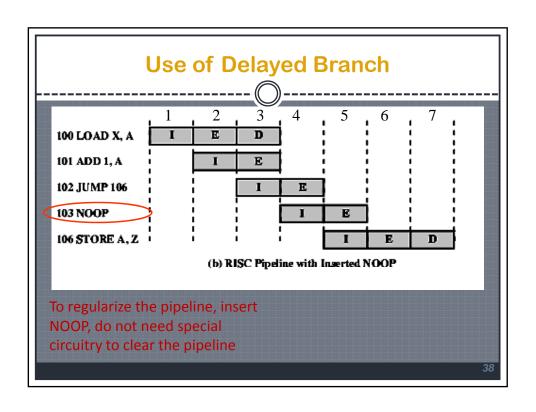

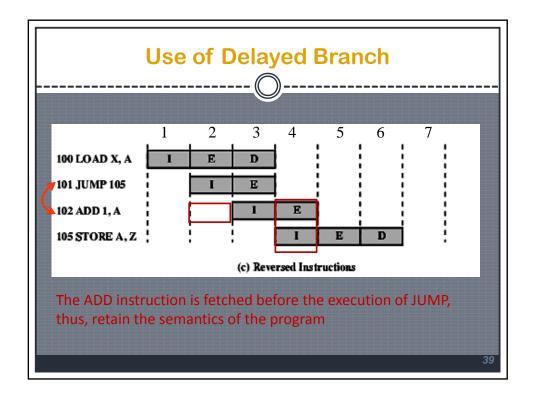

### **Optimization of Pipelining**

- Delayed branch

- Makes use of a branch that does not take effect until after execution of the following instruction.

- The instruction location immediately following the branch is referred to as the delay slot.

35

### **Normal and Delayed Branch** Address Normal Delayed **Optimized** 100 LOAD X,A LOAD X,A LOAD X,A ADD 1,A ADD 1,A 101 102 ADD A,B ADD A,B 103 SUB C,B 104 ADD A,B SUB C,B STORE A,Z SUB C,B STORE A,Z 105 106 STORE A,Z

# Homework Review Questions: 13.2 Hand in 29<sup>th</sup> Nov.