### 7.1 宏功能模块概述 算术组件 果加器、加法器、乘法器和LPM算术函数 门电略 多路复用器和LPM门函数 1/0组件 附钟数据恢复(CDR)、锁相环(PLL)、双数据速率(DDR)、干兆位收发器块(GXB)、LVDS接收器和发送器、PLL重新配置和远程更新宏功能模块 存储器编译器 FIFO Partitioner、RAM和ROM宏功能模块 存储组件 存储器、移位寄存器宏模块和LPM存储器函数

| 7.1 宏功能模块概述               |            |

|---------------------------|------------|

| 7.1.1 知识产权核的应用            |            |

| AMPP <b>程序</b> MegaCore函数 |            |

| OpenCore <b>评估功能</b>      |            |

| OpenCore Plus硬件评估功能       |            |

| 3                         | 、廉芯科技<br>X |

## 7.1 宏功能模块概述 7.1.2 使用MegaWizard Plug-In Manager - 输出文件>.bsf: Block Editor中使用的宏功能模块的符号(元件)。 - 输出文件>.cmp: 组件申明文件。 - 输出文件>.inc: 宏功能模块包装文件中模块的AHDL包含文件。 - 输出文件>.inc: 宏功能模块包装文件中模块的AHDL包含文件。 - 输出文件>.tdf: 要在AHDL设计中实例化的宏功能模块包装文件。 - 输出文件>.bv; VerilogHDL设计中实例化的宏功能模块包装文件。 - 输出文件>.bv; VerilogHDL设计中实例化的宏功能模块包装文件。 - 输出文件>.bv; VerilogHDL设计为用宏功能模块包装文件。 - 输出文件>.bv; VerilogHDL设计为用宏功能模块包装文件中模块的空体成 black-box申明,用于在使用EDA综合工具时指定端口方向。 - 输出文件> inst.tdf: 宏功能模块包装文件中子设计的AHDL例化示例。 - 输出文件> inst.vhd: 宏功能模块包装文件中字体的VHDL例化示例。 - 输出文件> inst.vhd: 宏功能模块包装文件中模块的VerilogHDL例化示例。 - 输出文件> inst.vhd: 宏功能模块包装文件中模块的VerilogHDL例化示例。

### 7.1 宏功能模块概述 7.1.3 在QuartusII中对宏功能模块进行例化 1、在VerilogHDL和VHDL中例化 2、使用端口和参数定义 3、使用端口和参数定义生成宏功能模块 计数器 乘-累加器和乘-加法器 加法·减法器 RAM 乘法器 移位寄存器

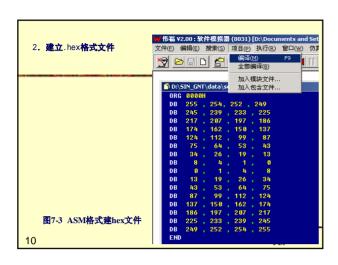

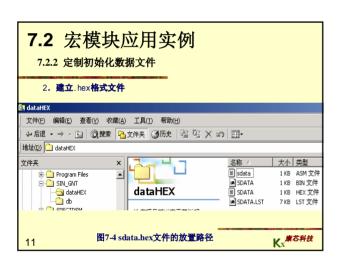

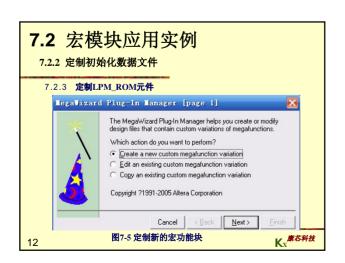

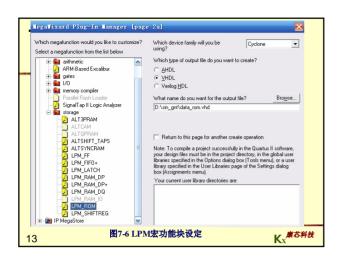

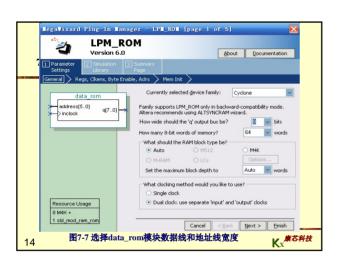

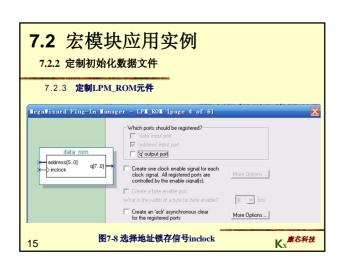

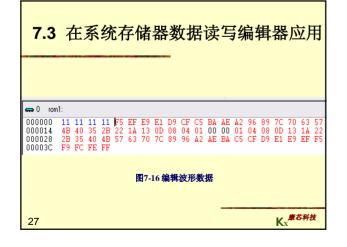

## 7.22 宏模块应用实例 7.2.2 定制初始化数据文件 1. 建立.mif格式文件 (例7-1) WIDTH = 8; DEPTH = 64; ADDRESS\_RADIX = HEX; DATA\_RADIX = HEX; CONTENT BEGIN 0 : FF; 1 : FE; 2 : FC; 3 : F9; 4 : F5; ... (数据略去) 3D : FC; 3E : FE; 3F : FF; END;

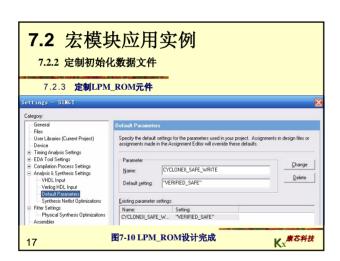

# 7.2.2 定制初始化数据文件 7.2.2 定制初始化数据文件 7.2.2 定制 DM DOM元件 Toggt Basard Plug-In Image or - LPI SQI [page 5 of 6] Do you want to specify the initial content of the memory? No. leave it blank. To data from or was the though content data to XXX on power up in simulation for the use the thought content of the memory content data to XXX on power up in simulation for the use the thought content file from the inclock The initial content it is should content of the memory inclock The initial content it is should content of the memory inclock The initial content it is should content to the power up in simulation file from the power up in simulation file from the use of the content inclock. The initial content it is should content to capture and update content inclock in the initial content in the ini

| 【例7-3】                                              |  |  |  |  |

|-----------------------------------------------------|--|--|--|--|

| LIBRARY ieee;                                       |  |  |  |  |

| USE ieee.std_logic_1164.all;                        |  |  |  |  |

| LIBRARY altera_mf;                                  |  |  |  |  |

| USE altera_mf.altera_mf_components.all;使用宏功能库中的所有元件 |  |  |  |  |

| ENTITY data_rom IS                                  |  |  |  |  |

| PORT (address : IN STD LOGIC VECTOR (5 DOWNTO 0);   |  |  |  |  |

| inclock : IN STD_LOGIC ;                            |  |  |  |  |

| q : OUT STD_LOGIC_VECTOR (7 DOWNTO 0) );            |  |  |  |  |

| END data rom;                                       |  |  |  |  |

| ARCHITECTURE SYN OF data_rom IS                     |  |  |  |  |

| SIGNAL sub wire0 : STD LOGIC VECTOR (7 DOWNTO 0);   |  |  |  |  |

| COMPONENT altsyncram例化altsyncram元件,调用了LPM模块         |  |  |  |  |

| altsyncram                                          |  |  |  |  |

| GENERIC (参数传递语句                                     |  |  |  |  |

| intended_device_family : STRING;类属参量数据类             |  |  |  |  |

| 型定义                                                 |  |  |  |  |

| width_a : NATURAL;                                  |  |  |  |  |

| widthad a : NATURAL;                                |  |  |  |  |

| numwords a : NATURAL;                               |  |  |  |  |

| operation mode : STRING;                            |  |  |  |  |

| outdata_reg_a : STRING;                             |  |  |  |  |

| address and a company of                            |  |  |  |  |

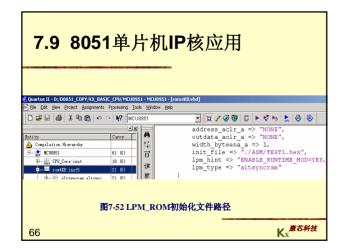

| address_acir_a : STRING; 接下页                        |  |  |  |  |

| 接上页                                                        |                     |

|------------------------------------------------------------|---------------------|

| <pre>lpm_hint =&gt; "ENABLE_RUN INSTANCE_NAME=NONE",</pre> | LPM类型               |

| 20                                                         | K <sub>X</sub> 康忘科技 |

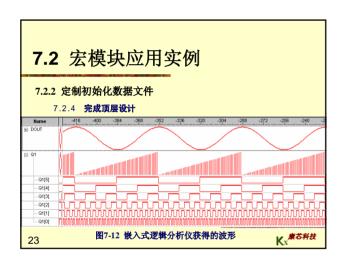

| 7.2.4 完成顶层设计                                                   |

|----------------------------------------------------------------|

|                                                                |

| 【例74】正弦信号发生器项层设计<br>LIBRARY IEEE;正弦信号发生器源文件                    |

| USE IEEE.STD LOGIC 1164.ALL;                                   |

| USE IEEE.STD LOGIC UNSIGNED.ALL;                               |

| ENTITY SINGT IS                                                |

| PORT ( CLK : IN STD LOGIC;信号源时钟                                |

| DOUT : OUT STD_LOGIC_VECTOR (7 DOWNTO 0) );8位波形数据输出            |

| END;                                                           |

| ARCHITECTURE DACC OF SINGT IS                                  |

| COMPONENT data_rom调用波形数据存储器LPM_ROM文件: data_rom.vhd声明           |

| PORT(address : IN STD_LOGIC_VECTOR (5 DOWNTO 0);6位地址信号         |

| inclock : IN STD_LOGIC ;地址锁存时钟                                 |

| q : OUT STD_LOGIC_VECTOR (7 DOWNTO 0) );                       |

| END COMPONENT;                                                 |

| SIGNAL Q1 : STD_LOGIC_VECTOR (5 DOWNTO 0);设定内部节点作为地址计数器        |

| BEGIN                                                          |

| PROCESS(CLK )LPM_ROM <b>地址发生器进程</b> BEGIN                      |

| IF CLK'EVENT AND CLK = '1' THEN Q1<=Q1+1;Q1作为地址发生器计数器          |

| END IF;                                                        |

| END PROCESS:                                                   |

| ul : data rom PORT MAP(address=>Q1, q => DOUT,inclock=>CLK);例化 |

| END;                                                           |

| ETW #                                                          |

| $K_{x}^{ROPTO}$                                                |

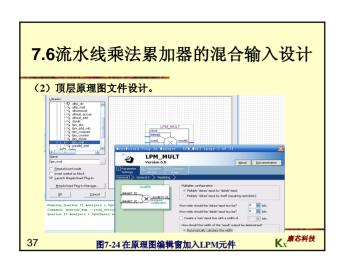

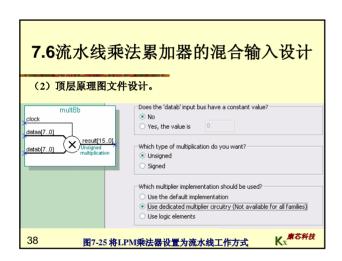

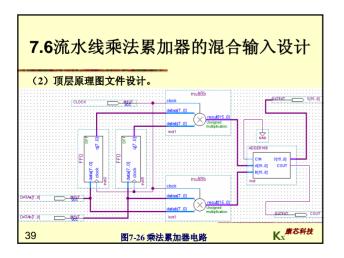

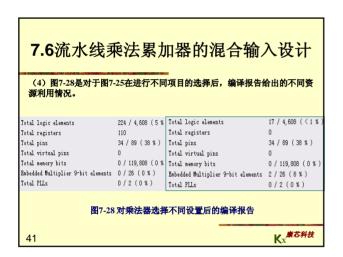

### 7.6流水线乘法累加器的混合输入设计 (1) 用VHDL设计16位加法器。 [例7-5] LIERRAY IEEE; USE IEEE.STD\_LOGIC\_1164.ALL; USE IEEE.STD\_LOGIC\_UNSIGNED.ALL; ENTITY ADDERIGE IS PORT (CIN: IN STD\_LOGIC, VECTOR(15 DOWNTO 0); S: OUT STD\_LOGIC\_VECTOR(15 DOWNTO 0); COUT: OUT STD\_LOGIC\_VECTOR(15 DOWNTO 0); END ADDERIGE; ARCHITECTURE behav OF ADDERIGE IS SIGNAL SINT: STD\_LOGIC\_VECTOR(16 DOWNTO 0); SIGNAL AB.B: STD\_LOGIC\_VECTOR(16 DOWNTO 0); BEGIN AA<='0'&A; BB<='0'& B; SINT <= AA + BB + CIN; S <= SINT(15 DOWNTO 0); COUT <= SINT(4); END behav; 36

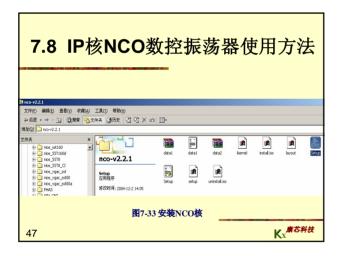

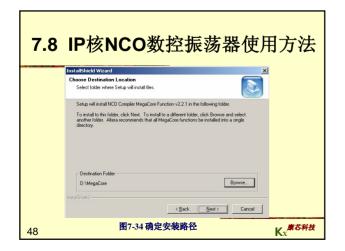

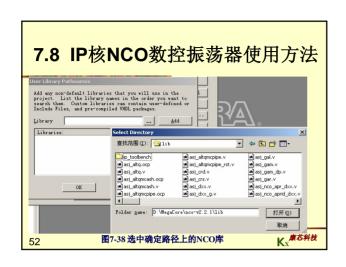

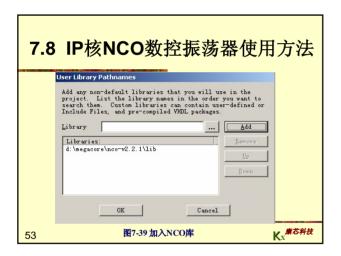

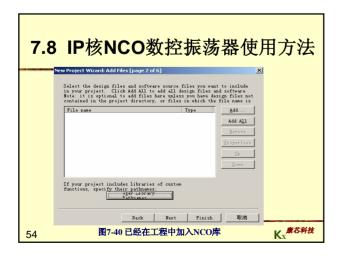

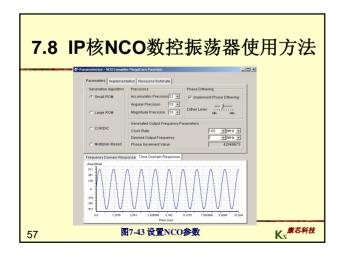

# 7.8 IP核NCO数控振荡器使用方法 \*\*Countral IP \*\*Countral IP \*\*Country | Dolls Window Delig | Dolls | Do

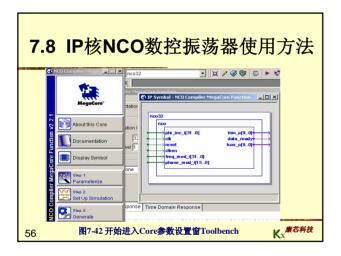

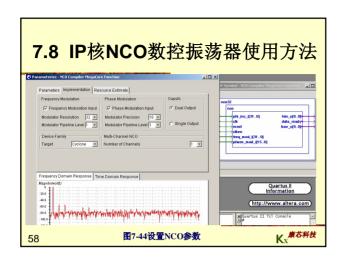

# 7.8 IP核NCO数控振荡器使用方法 \*\*MegaWizard Fluy-In Manager [page 20] \*\*Which segafunction would you like to Select a negafunction from the list | Which device family will | Cyclone | which there sold the segafunction from the list | Which device family will | Cyclone | which there is common actions | which type of output file do you want to | MIL | MI

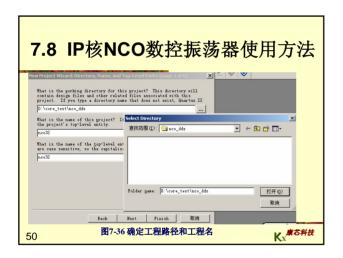

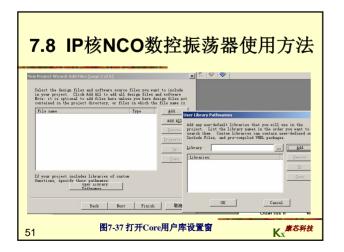

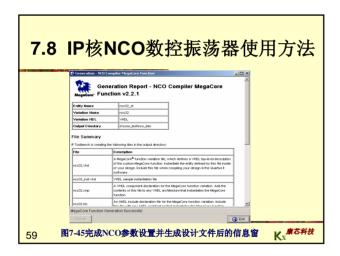

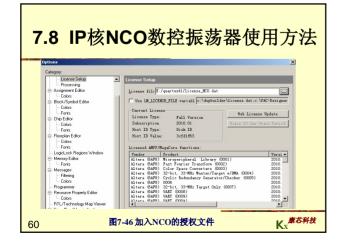

## 7.8 IP核NCO数控振荡器使用方法 \*\*\*Gounten II-diverse\_instance\_deformations\_records\*\* Fig. Est 19mm Propert Bridgements Properting 10mm Properting 10mm

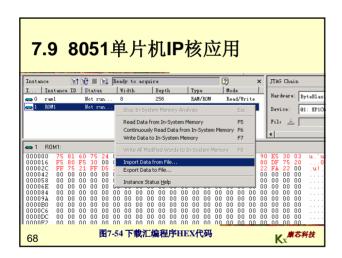

|                  |         | ORG           |                     |

|------------------|---------|---------------|---------------------|

|                  | MAIN :  | MOV SP,#60H   |                     |

|                  |         | MOV 24H,#89H  |                     |

|                  |         | MOU 30H,#01H  |                     |

|                  | ROUND:  | LCALL DELAY1  |                     |

|                  |         | MOV A,24H     |                     |

|                  |         | INC A         |                     |

|                  | _       | MOV 24H,A     |                     |

|                  |         | MOV P1,A      |                     |

|                  |         | MOV A,39H     |                     |

|                  |         | RR A          |                     |

|                  |         | MOV PO,A      |                     |

|                  |         | MOV 30H,A     |                     |

|                  |         | NOP           |                     |

|                  |         | NOP           |                     |

|                  |         | MOV A,P8      |                     |

|                  |         | MOV B,P3      |                     |

|                  |         | ADD A,B       |                     |

|                  |         | MOV P2,A      |                     |

|                  |         | LCALL DELAY1  |                     |

| 图7-53 TEST1.asm汇 |         | SJMP ROUND    |                     |

|                  | DELAY:  | MOV 20H,#0FFH |                     |

| 编程序              | W1 :    | MOV 21H,#0FFH |                     |

|                  | W2 :    | DJNZ 21H,W2   |                     |

|                  |         | DJNZ 20H,W1   |                     |

|                  |         | RET           |                     |

|                  | DELAY1: | MOV 22H,#08H  |                     |

|                  | W3 :    | LCALL DELAY   |                     |

|                  |         | DJNZ 22H,W3   |                     |

| 67               |         | RET           | K <sub>x</sub> 廣芯科技 |

| 67               |         | END           | X                   |

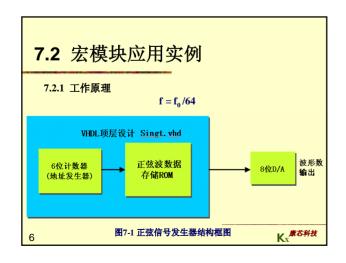

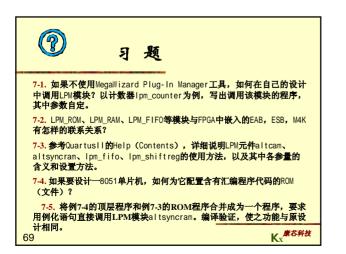

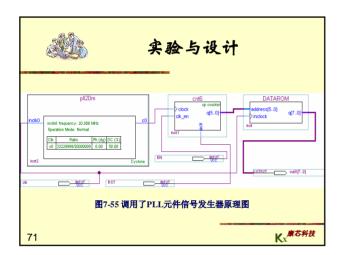

### 7-1. 正弦信号发生器设计

- (1) <mark>实验目的:</mark> 进一步熟悉QuartusII及其LPM\_ROM与FPGA硬件资源的使用方法。

- (2) 实验原理:参考本章相关内容。

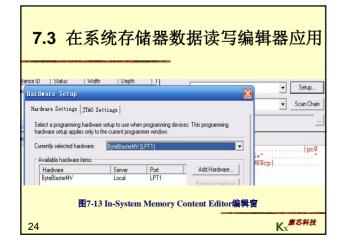

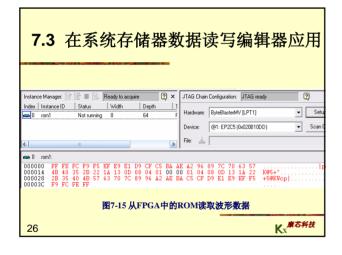

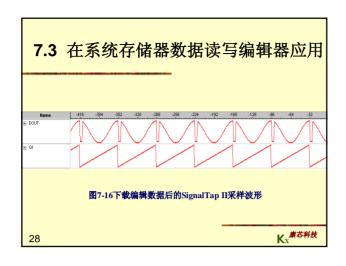

- (3) 实验内容1:根据例7-4,在Quartus II上完成正弦信号发生器设计,包括仿真和资源利用情况了解(假设利用Cyclone器件)。最后在实验系统上实测,包括SignalTap II测试、FPGA中ROM的在系统数据读写测试和利用示波器测试。最后完成EPCSx配置器件的编程。

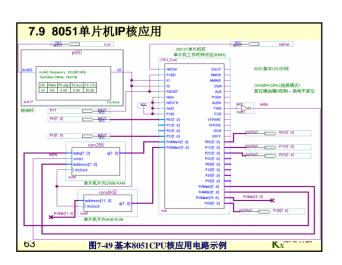

- (4) 实验内容2: 按照图7-49所示,用原理图方法设计正弦信号发生器,要调用3个LPM模块来构成: 1、PLL,输入频率20MHz, 32MHz单频率输出: 2、6位二进制计数器; 3、LPM ROM,加载的波形数据同上。注意,硬件实现时可以通过SignalTapII观察波形,但不能用0832输出,波形必须用高速DAC输出。

70 **K**x<sup>康艺科5</sup>

### 实验与设计

### 7-1. 正弦信号发生器设计

- (5) 实验内容3, 修改例7-3的数据ROM文件,设其数据线宽度为8, 地址线宽度也为8, 初始化数据文件使用MIF格式,用C程序产生正弦信号数据,最后完成以上相同的实验。

- (6) 实验内容4. 设计一任意波形信号发生器,可以使用LPM双口RAM担任波形数据存储器,利用单片机产生所需要的波形数据,然后输向FPGA中的RAM(可以利用GW48系统上与FPGA接口的单片机完成此实验,D/A可利用系统上配置的0832或5651高速器件)。

- (7) <mark>实验报告:</mark> 根据以上的实验内容写出实验报告,包括设计原理、程序设计、程序分析、仿真分析、硬件测试和详细实验过程。

72 K<sub>x</sub> <del>康</del>芯科技

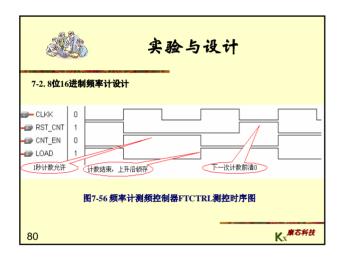

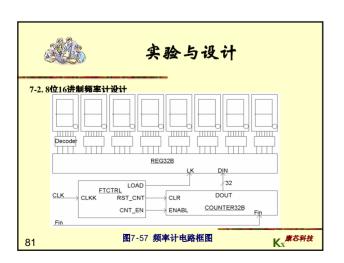

### 7-2.8位16进制频率计设计

- (1) 实验目的:设计8位16进制频率计,学习较复杂的数字系统设计方法。

- (2) 实验原理:根据频率的定义和频率测量的基本原理,测定信号的频率必须有一个脉宽为1秒的输入信号脉冲计数允许的信号; 1秒计数结束后,计数值被锁入锁存器,计数器清0,为下一测频计数周期作好准备。测频控制信号可以由一个独立的发生器来产生,即图7-57中的FTCTRL。根据测频原理,测频控制时序可以如图7-56所示。

理,测测控制时序可以知图(7-0月/不。 设计要求是: FTCTRL的计数使能信号CNT\_EN能产生一个I秒脉宽的周期信号,并 对频率计中的32位二进制计数器COUNTER32B(图7-57)的ENABL使能端进行同 步控制。当CNT\_EN高电平时允许计数:低电平时停止计数,并保持其所计的脉冲 数。在停止计数期间,首先需要一个锁存信号LOAD的上跳沿将计数器在前1秒钟的 计数值锁存进锁存器FEG33B中,并由外部的16进制7段译码器译出,显示计数值。 设置锁存器的好处是数据显示稳定,不会由于周期性的海心等一间不断闪烁。锁存信 号后,必须有一清0信号RST\_CNT对计数器进行清零,为下1秒的计数操作作准备。 73

### 实验与设计

### 7-2.8位16进制频率计设计

- (3) 实验内容1:分别仿真测试模块例7-7、例7-8和例7-9,再结合例7-10完成 频率计的完整设计和硬件实现,并给出其测频时序波形及其分析。建议选实验电路模式5;8个数码管以16进制形式显示测频输出,特测频率输入FIN由clockl输入,频率可选4Hz、25cHZ、3Hz...50MHz等;1HZ测频控制信号CLK1HZ可由clock2输入(用跳线选1Hz)。注意,这时8个数码管的测频显示值是16进制的。

- (4) 实验内容2: 参考例4-22, 将频率计改为8位10进制频率计, 注意此设计 电路的计数器必须是8个4位的10进制计数器, 而不是1个。此外注意在测频 速度上给予优化。

- (5) 实验内容3: 用LPM模块取代例7-8和例7-9,再完成同样的设计任务。

- (6) 实验报告:给出频率计设计的完整实验报告。

74

Kx 糜芯科技

| LIRRARY IEEE; 测频控制电路 USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY FTCTRL IS POPT (CLK: IN STD_LOGIC: 1Hz |

|----------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                  |

| CNT_EN : OUT STD_LOGIC; 计数器附钟使能 RST CNT : OUT STD LOGIC; 计数器清零                                                                   |

| RSI_CNI: OUT SID_LOGIC; N気器情令<br>Load: OUT STD LOGIC ); 輸出額存信号                                                                   |

| END FTCTRL:                                                                                                                      |

| ARCHITECTURE behav OF FTCTRL IS                                                                                                  |

| SIGNAL Div2CLK : STD LOGIC:                                                                                                      |

| BEGIN                                                                                                                            |

| PROCESS( CLKK )                                                                                                                  |

| BEGIN                                                                                                                            |

| IF CLKK'EVENT AND CLKK = '1' THEN 1Hz <b>时钟</b> 2分類 Div2CLK <= NOT Div2CLK;                                                      |

| END IF;                                                                                                                          |

| END PROCESS;                                                                                                                     |

| PROCESS (CLKK, Div2CLK)                                                                                                          |

| BEGIN                                                                                                                            |

| IF CLKK='0' AND Div2CLK='0' THEN RST_CNT<='1'; 产生计数器清零信                                                                          |

| 号                                                                                                                                |

| <pre>ELSE RST_CNT &lt;= '0'; END IF;</pre>                                                                                       |

| END PROCESS;                                                                                                                     |

| Load <= NOT Div2CLK; CNT_EN <= Div2CLK; 康芯科技 Not Div2CLK; Kx                                                                     |

```

【例7-8】

LIBRARY IEEE; --32位锁存器

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY REG32B IS

PORT (

LK : IN STD_LOGIC;

DIN : IN STD_LOGIC_VECTOR(31

DOWNTO 0);

DOUT : OUT STD_LOGIC_VECTOR(31

DOWNTO 0) );

END REG32B;

ARCHITECTURE behav OF REG32B IS

BEGIN

PROCESS(LK, DIN)

BEGIN

IF LK'EVENT AND LK = '1' THEN DOUT <= DIN;

END IF;

END PROCESS;

Kx 康芯科技

76ND behav;

```

```

【例7-9】

LIBRARY IEEE; --32位计数器

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

TY COUNTER32B IS

PORT (FIN: IN STD_LOGIC; -- 附钟信号

CLR: IN STD_LOGIC; -- 清零信号

ENABL: IN STD_LOGIC; -- 计数使能信号

DOUT: OUT STD_LOGIC_VECTOR(31 DOWNTO 0)); -- 计数结果

END COUNTER32B;

ARCHITECTURE behav OF COUNTER32B IS

SIGNAL CQI : STD_LOGIC_VECTOR(31 DOWNTO 0);

BEGIN

PROCESS(FIN, CLR, ENABL)

END IF;

END PROCESS:

DOUT <= CQI;

END behav;

Kx 康芯科技

77

```

```

LIBRARY IEEE; --頻率计项层文件

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY FREQTEST IS

FORT ( CLKIHZ : IN STD_LOGIC;

FSIN : IN STD_LOGIC;

DOUT : OUT STD_LOGIC_VECTOR(31 DOWNTO 0) );

END FREQTEST;

ARCHITECTURE struc OF FREQTEST IS

COMPONENT FTCTRL

FORT (CLKK : IN STD_LOGIC; -- 计数器时钟使能

RST_CNT : OUT STD_LOGIC; -- 计数器消零

Load : OUT STD_LOGIC ); -- 输出锁存信号

END COMPONENT;

COMPONENT COUNTER32B

FORT (FIN : IN STD_LOGIC; -- 清零信号

ENABL : IN STD_LOGIC; -- 计数使能信号

DOUT : OUT STD_LOGIC; -- 计数使能信号

DOUT : OUT STD_LOGIC; -- 计数使能信号

ENABL : IN STD_LOGIC; -- 计数使能信号

DOUT : OUT STD_LOGIC_VECTOR(31 DOWNTO 0)); -- 计数结果

END COMPONENT;

```

```

COMPONENT REG32B

PORT ( LK : IN STD_LOGIC;

DIN : IN STD_LOGIC VECTOR(31 DOWNTO 0);

DOUT : OUT STD_LOGIC_VECTOR(31 DOWNTO 0) );

END COMPONENT;

SIGNAL TSTEN1 : STD_LOGIC;

SIGNAL CLACIT1 : STD_LOGIC;

SIGNAL CLACIT1 : STD_LOGIC;

SIGNAL DTO1 : STD_LOGIC (STONAL DOWNTO 0);

SIGNAL CARRY_OUT1 : STD_LOGIC_VECTOR(6 DOWNTO 0);

BEGIN

U1 : FTCTRL PORT MAP(CLKK =>CLK1HZ,CNT_EN=>TSTEN1,

RST_CNT =>CLR_CNT1,Load =>Load1);

U2 : REG32B PORT MAP( LK => Load1, DIN=>DTO1, DOUT =>

DOUT);

U3 : COUNTER32B PORT MAP( FIN => FSIN, CLR => CLR_CNT1,

ENABL => TSTEN1, DOUT=>DTO1 );

END struc;

```

### 7-3. 利用LPM\_ROM设计乘法器

(1) 实验原理:硬件乘法器有多种设计方法,但相比之下,由LPM\_ROM构成的乘法表方式的乘法器的运算速度量快。这里定制LPM\_ROM的地址位宽为8;地址输入由时钟inclock的上升沿锁入;数据位宽也为8。最后为ROM配置乘法表数据文件。

LPM\_ROM中作为乘法表的数据文件rom\_data.mif如例7-11所示。其中的地址/数据表达方式是,冒号左边写ROM地址值,冒号右边写对应此地址放置的16进制数据。如47:28,表示47为地址,28为该地址中的数据,这样,地址高4位和低4位可以分别看成是乘数和被乘数,输出的数据可以看成是它们的乘积。

82

Kx 康芯科技

###

### 实验与设计

### 7-3. 利用LPM\_ROM设计乘法器

(2) 实验内容,利用LPM\_ROM设计4X4和8X8乘法器各一个,再利用 VHDL语言描述,由逻辑宏单元构成同类乘法器各一,比较这两类乘法器的 运行速度和资源耗用情况。

84

Kx 康芯科技

### 7.4 TD核应用实验

利用IP核完成如下2项设计:

- 1、利用NCO核分别设计:

- (1) FSK; (2) PSK; (3) DDS; (4) 移相信号发生器; (5) 扫频信号源; (6) 全数字式锁相环。

- 2、利用NCO和FIR核设计数字正交调制解调器(参考清华大学出版社 《SOPC技术实用教程》中的实验6-5)。

85

Kx 康芯科技

### 实验与设计

### 7-5.8051单片机IP核应用实验

- (1) 实验内容1,参考7.9节,在图7-49所示的基本电路平台上增加一些LPM 或VHDL表述硬件模块(如锁存器、译码器、PWM发生器、A/D采样控制 模块、液晶控制模块等),及与单片机的接口电路,利用单片机进行控 制,再编辑对应的汇编软件,完成进一步的实验。

- (2) <mark>实验内容</mark>2: 选择不同模式,和引脚锁定情况,协调软件与硬件设计,完成较大的软硬件综合设计模块。

- (3) 实验内容3:编辑一段用于测试的汇编程序,利用时序仿真和逻辑分析 仪,了解8051单片机的数据总线、指令总线、不同指令执行、地址总线、 ALE、PSEN、个10端口、不同指令对应下的端口方向控制信号P0E、 P1E、P2E、P3E等信号间的时序情况,给出分析报告。

86

Kx 康芯科技