九十二學年度

電子工程研判所

系(所)

組碩士班研究生招生考試

科目

固態電子元件

科號

2605

共

ス

頁第

/

頁 \*請在試卷【答案卷】內作答

- 1. For a MOS capacitor fabricated on p-type silicon substrate and with a SiO<sub>2</sub> thickness of d, draw the schematic diagrams of the following items under the condition of strong inversion: (1) energy band diagram of the three materials (metal, SiO<sub>2</sub>, and Si) and mark the conduction band edge E<sub>C</sub>, valence band edge E<sub>V</sub>, intrinsic Fermi level E<sub>i</sub>, and Fermi level E<sub>F</sub> of the semiconductor, (2) schematic diagram of the charge distribution, (3) schematic diagram of the electric field distribution, (4) schematic diagram of the electrostatic potential distribution. Use x as the horizontal axis for all the four diagrams. (20%)

- 2. The threshold voltage of a metal-oxide-semiconductor field effect transistor (MOSFET) is usually expressed as the sum of four terms. (1) Write down the expression of the threshold voltage of a MOSFET. Explain the meaning of each term. (2) For typical n-channel and p-channel MOSFETs, what is the polarity of each term (i.e., whether they are positive or negative)? (15%)

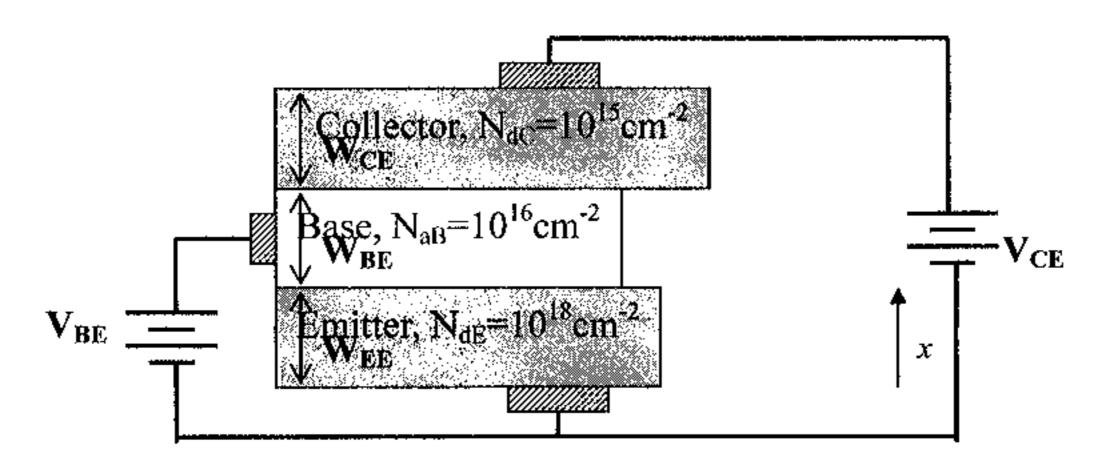

- 3. A npn BJT with doping level label in the Figure shown below. Let n<sub>i</sub>=1x10<sup>10</sup>cm<sup>-3</sup>, V<sub>T</sub>ln10=60mV, W<sub>E</sub>=0.1µm, W<sub>B</sub>=0.2µm, W<sub>C</sub>=0.5µm. Assume ohmic contact at the metal/semiconductor interface. (a) Plot the energy-band diagram, minority carrier densities, n(x) and p(x) and electric field, E(x), at thermal equilibrium when V<sub>BE</sub>=V<sub>CE</sub>=0. Label the position of the fermi level and values of n(x), p(x) at the boundaries. (10%) (b) Plot the energy-band diagram, minority carrier densities, n(x) and p(x) and electric field E(x) at thermal equilibrium when V<sub>BE</sub>=0.6V, V<sub>CE</sub>=1.5V. Label the position of the fermi level and values of n(x), p(x)at the boundaries. (10%) (c) Discuss respectively how the current gain, β, of this device changes when N<sub>dE</sub> increases/ W<sub>E</sub> increases? (5%)

## 國 立 清 華 大 學 命 題 紙

|     | 九十二學年度 | 電子工程研判所 | _系(所)_ | <br>組碩士班研究生招生考試     |   |

|-----|--------|---------|--------|---------------------|---|

| 科目_ | 固態電子元件 | 科號 2605 | _ 共    | <br>頁 *請在試卷【答案卷】內作答 | 奎 |

## **4. JFET**

- (a) Plot the cross-section of a JFET device that can be realized in CMOS single-well technology on p-type substrate. (5%)

- (b) How will the substrate bias affect the pinch-off voltage, V<sub>P</sub>? (5%)

- 5. Plot (5%) and explain briefly (10%) the temperature dependence of carrier mobility in semiconductor materials.

- 6. What is a (a) one-sided junction (5%); (b) linear graded junction (5%): and (c) hyper-abrupt junction (5%)?