# IMPACT OF MANUFACTURING FLOW ON YIELD LOSSES IN NANOSCALE FABRICS

A Thesis Presented

by

## PRIYAMVADA VIJAYAKUMAR

Submitted to the Graduate School of the University of Massachusetts Amherst in partial fulfillment of the requirements for the degree of

MASTER OF SCIENCE IN ELECTRICAL AND COMPUTER ENGINEERING

February 2012

Department of Electrical and Computer Engineering

© Copyright by Priyamvada Vijayakumar2012

All Rights Reserved

# IMPACT OF MANUFACTURING FLOW ON YIELD LOSSES IN NANOSCALE FABRICS

## A Thesis Presented

by

## PRIYAMVADA VIJAYAKUMAR

| Approved as to style and content by: |  |

|--------------------------------------|--|

|                                      |  |

| Israel Koren, Co-chair               |  |

|                                      |  |

| C. M. Krishna, Co-chair              |  |

| Csaba A. Moritz, Member              |  |

| Couda 13. MOIRE, MCHIOCI             |  |

|                                      |  |

C.V. Hollot, Department Head

Department of Electrical and Computer Engineering

#### **ACKNOWLEDGEMENTS**

I take this opportunity to thank all the people who have helped me with my thesis. First and foremost, I thank my advisor, Prof. Israel Koren for his supervision, inspiration, encouragement and support. I would like to extend my gratitude to the committee members, Prof. Mani Krishna and Prof. Csaba Andras Moritz for their time, advice and suggestions throughout this project. I would like to thank all my lab mates for their encouragement. Special Thanks to my mentor, Pritish Narayanan for being my inspiration and guiding me throughout the course of my thesis. Finally, I would love to thank my family, my friends and colleagues from IBM for their constant support and motivation through this journey.

#### **ABSTRACT**

## IMPACT OF MANUFACTURING FLOW ON YIELD LOSSES IN NANOSCALE FABRICS

#### FEBRUARY 2012

#### PRIYAMVADA VIJAYAKUMAR

## B.E, VISHVESHWARIAH TECHNOLOGICAL UNIVERSITY

## M.S.E.C.E., UNIVERSITY OF MASSACHUSETTS AMHERST

Directed by: Professor Israel Koren

Reliable and scalable manufacturing of nanofabrics entails significant challenges. Scalable nano-manufacturing approaches that employ the use of lithographic masks in conjunction with nanofabrication based on self-assembly have been proposed. A bottom-up fabrication of nanoelectronic circuits is expected to be subject to various defects and identifying the types of defects that may occur during each step of a manufacturing pathway is essential in any attempt to achieve reliable manufacturing. This thesis aims at analyzing the sources of defects in a nanomanufacturing flow and estimating the resulting yield loss. It integrates physical fabric considerations, manufacturing sequences and the resulting defect scenarios. This is in contrast to most current approaches that use conventional defect models and assume constant defect rates without analyzing the manufacturing pathway to determine the sources of defects and their probabilities. The manufacturing pathway will be analyzed for identifying the defects introduced during each manufacturing step in the sequence, followed by yield loss estimation.

## TABLE OF CONTENTS

|                                                                                 | Page |

|---------------------------------------------------------------------------------|------|

| ACKNOWLEDGEMENTS                                                                | iv   |

| ABSTRACT                                                                        | v    |

| LIST OF FIGURES                                                                 | viii |

| CHAPTER                                                                         |      |

| 1. INTRODUCTION                                                                 | 1    |

| 1.1 Organization                                                                | 3    |

| 1.2 Overview of NASIC's                                                         |      |

| 1.3 Overview of WISP-0                                                          | 5    |

| 2. RELATED WORK                                                                 | 6    |

| 2.1 Introduction                                                                | 6    |

| 2.2 Fault tolerance in nanofabrics.                                             | 6    |

| 2.3 Fault model assumed                                                         | 7    |

| 2.4 Built-in Fault-Tolerance in NASICs: Circuit-Level and Structural Redundancy |      |

| 2.5 Voting at Nanoscale                                                         | 9    |

| 3. YIELD MODELING                                                               | 11   |

| 3.1 Introduction                                                                | 11   |

| 3.2 Manufacturing Pathway                                                       |      |

| 3.3 Analysis                                                                    | 14   |

| 4. RANDOM DEFECT BASED YIELD                                                    | 16   |

| 4.1 Introduction                                                                | 16   |

| 4.2 Methodology Followed                                                        | 17   |

| 4.3 Simulation Results                                                          |      |

| 4.4 Conclusion                                                                  | 23   |

| 5. SYSTEMATIC YIELD LOSS IN NANOSCALE FABRICS                                   | 25   |

| 5.1Introduction.                                                                |      |

| 5.1.1 Mask Offset and Overlay                                                   |      |

| 5.1.1.1 Implications of varying feature size on systematic yield                | 26   |

| 5.1.2 Nanowire Alignment.                                  | 27 |

|------------------------------------------------------------|----|

| 5.2 Analysis                                               | 28 |

| 5.3 Modeling Approach                                      | 32 |

| 5.3.1 Lithographic Mask – Overlay Modeling                 |    |

| 5.3.1.1 Modeling of Mask Overlay                           | 32 |

| 5.3.1.2 Modeling of mask feature size                      |    |

| 5.3.2 Modeling of Nanowire Transfer                        |    |

| 5.4 Experiments and Results                                | 36 |

| 5.4.1 Mask Overlay and Registration                        |    |

| 5.4.1.1 Sensitivity to pitch                               |    |

| 5.4.1.2 Sensitivity to width                               | 39 |

| 5.4.1.3 Sensitivity to mask feature size                   | 41 |

| 5.4.2 'Nanowire transfer' implications on Systematic Yield | 44 |

| 5.5. Conclusion                                            | 46 |

| 6. OVERALL YIELD ESTIMATION                                | 48 |

| 7. CONCLUSION                                              | 52 |

| RIRI IOGRAPHY                                              | 54 |

## LIST OF FIGURES

| Figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Page     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

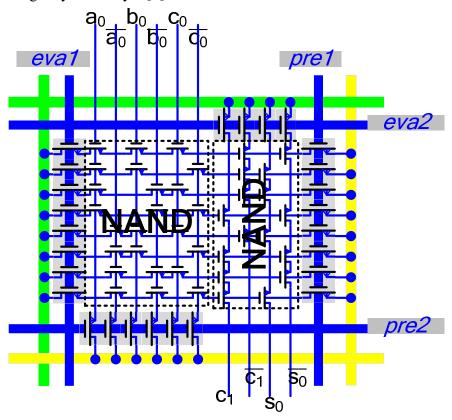

| 1 1-bit Full adder using NASICs [8]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

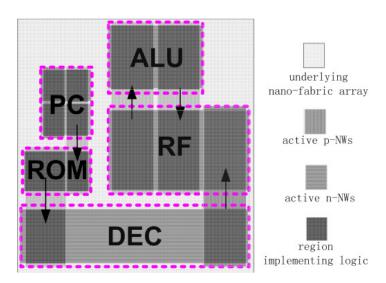

| 2 WISP-0 Floorplan [14]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5        |

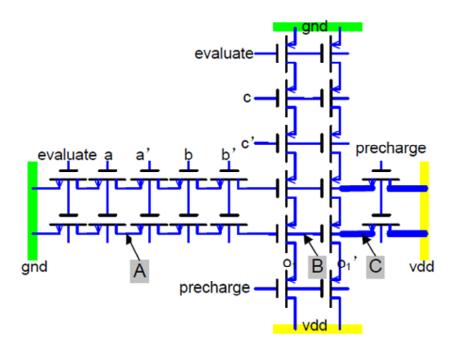

| 3 Simple 2-way structural redundancy [14]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9        |

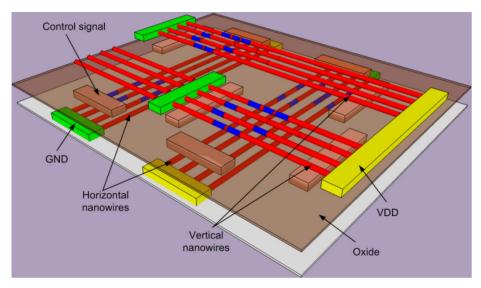

| 4 NASIC Fabric [16]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12       |

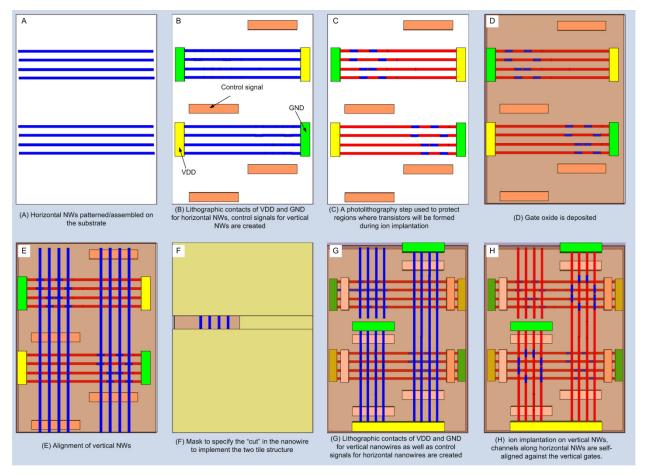

| 5 NASIC's manufacturing sequence using "two nanowire transfer" [16]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 13       |

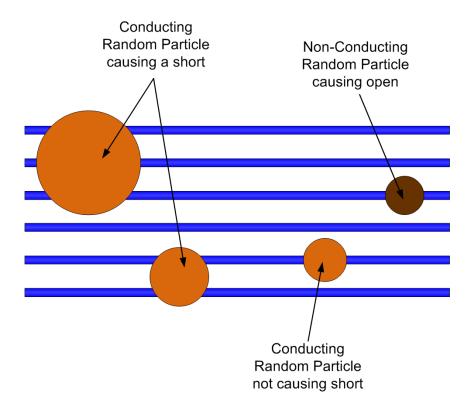

| 6 Particulate defects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 17       |

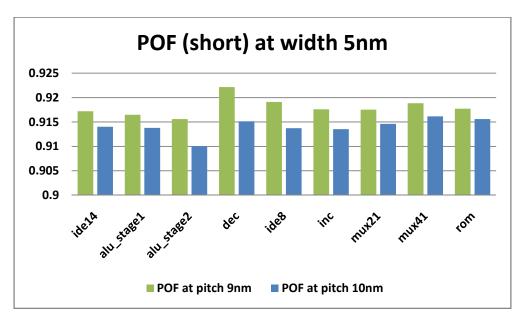

| 7 POF for shorts at 5nm width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 20       |

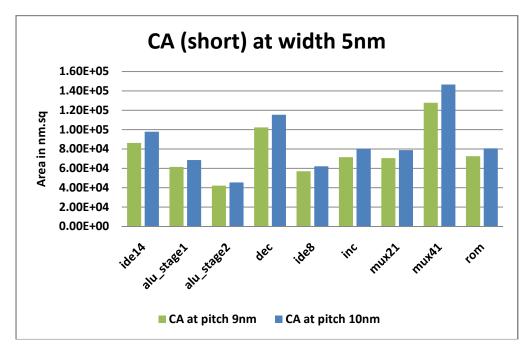

| 8 CA for short at 5nm width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 20       |

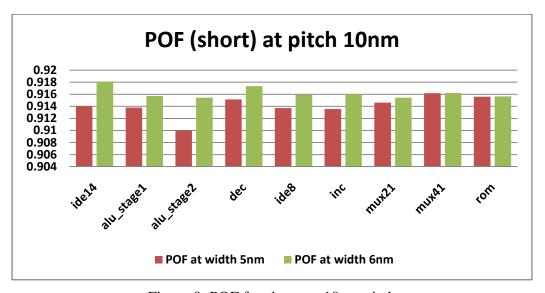

| 9 POF for shorts at 10nm pitch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 21       |

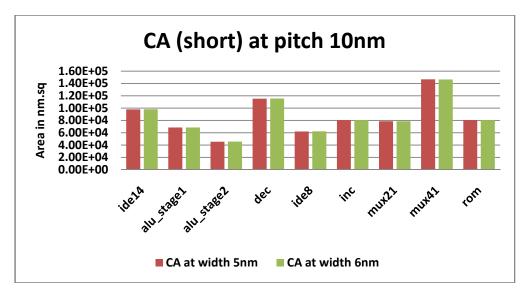

| 10 CA for shorts at 10nm pitch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 22       |

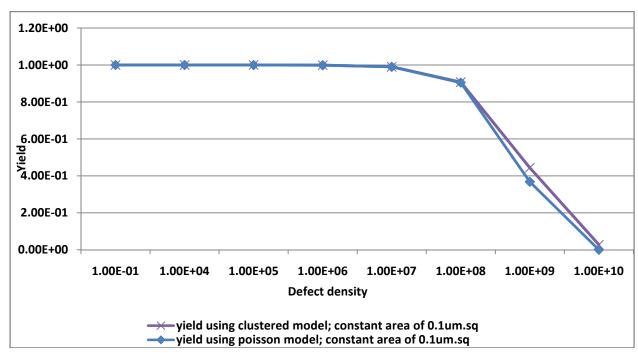

| 11 Variation of random defect limited yield with defect density                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 22       |

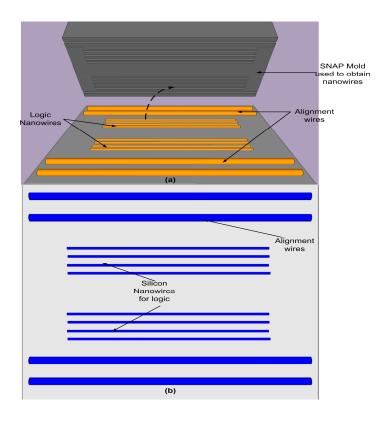

| 12 NIL technique showing both the nanowires and the alignment markers in the same mold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 29       |

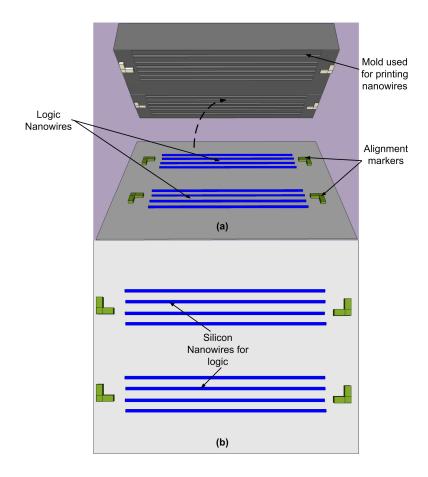

| 13 SNAP technique, showing patterned nanowires (different dimension than logic nanowires) who will be shown that the showing patterned nanowires (different dimension than logic nanowires) who is a simple shown that the showing patterned nanowires (different dimension than logic nanowires) who is a simple shown that the | hich can |

| be used as alignment markers for moiré patterning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 30       |

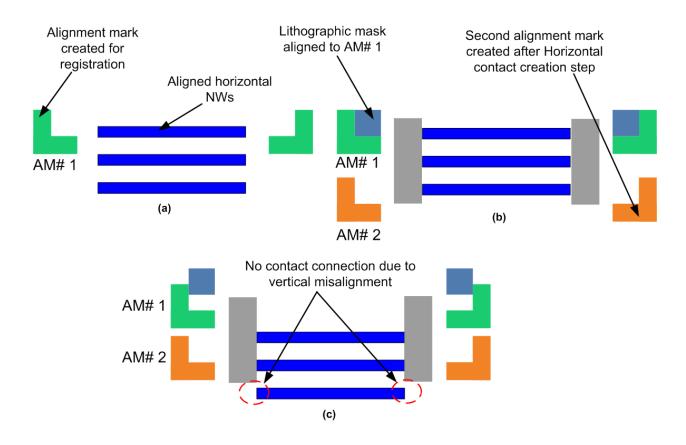

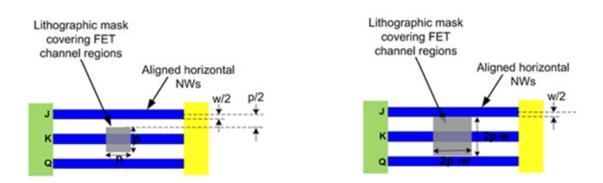

| 14 Depiction of mask registration during "horizontal contact creation" step                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 31       |

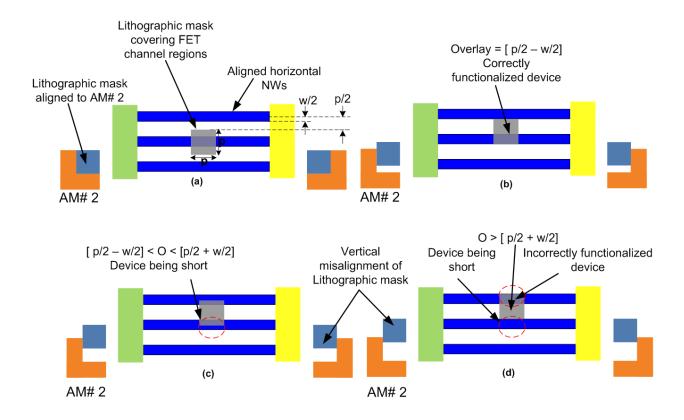

| 15 Depiction of the mask overlay effect during the "Horizontal Functionalization" step                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 32       |

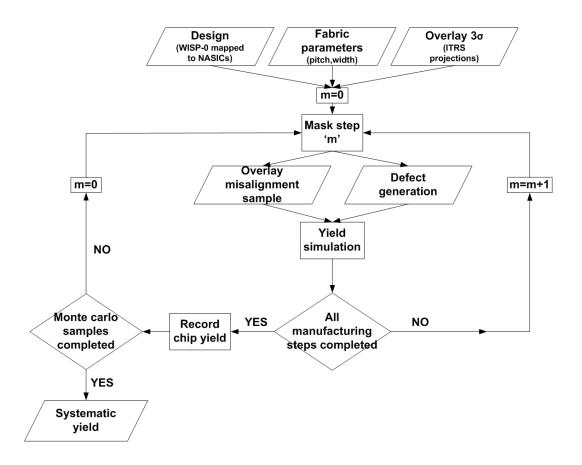

| 16 Procedure for yield estimation to predict the systematic yield loss due to mask overlay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 33       |

| 17 Mask feature size of dimension (a) (pitch) X (pitch) (b) (2p - w) X (2p - w)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

| 18 Overlay values as projected by ITRS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 36       |

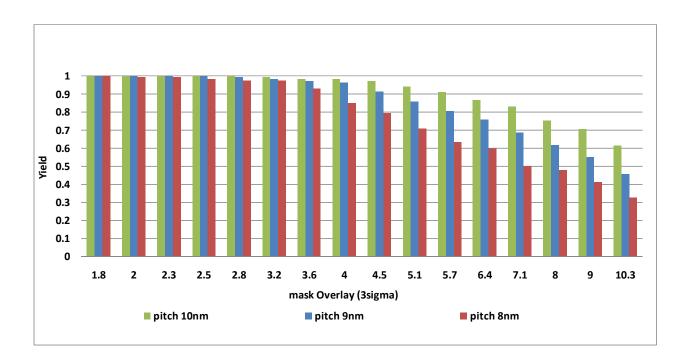

| 19 Variation in yield for width of 5nm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 38       |

| 20 Variation in effective yield for width of 5nm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

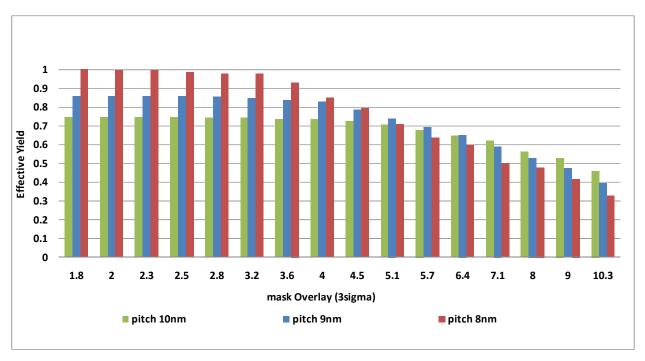

| 21 Variation in yield for nanowire pitch of 10nm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 39       |

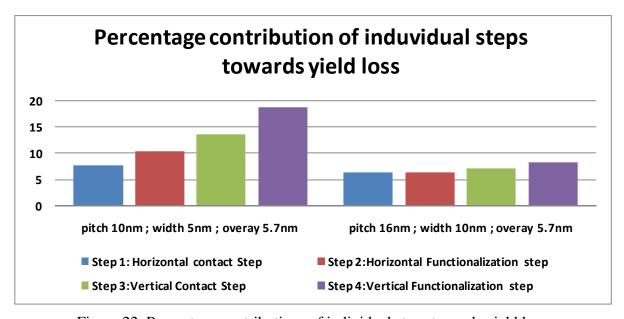

| 22 Percentage contributions of individual steps towards yield loss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 41       |

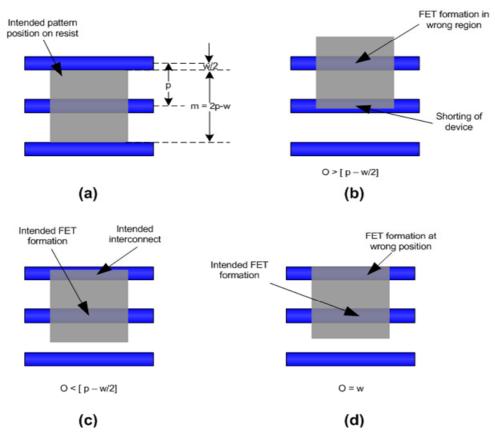

| 23 Implication of mask overlay with mask feature size of dimension $(2p - w) \ X \ (2p - w) \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 43       |

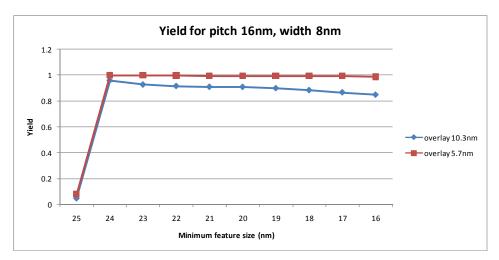

| 24 Yield for varying mask feature size, pitch 16nm, width 8nm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 44       |

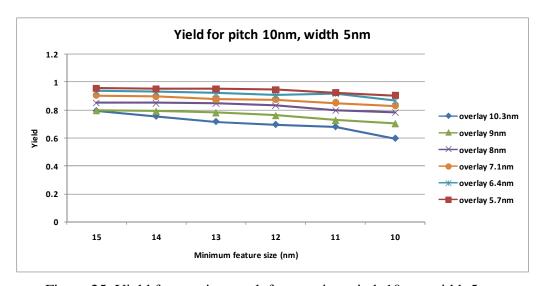

| 25 Yield for varying mask feature size, pitch 10nm, width 5nm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 44       |

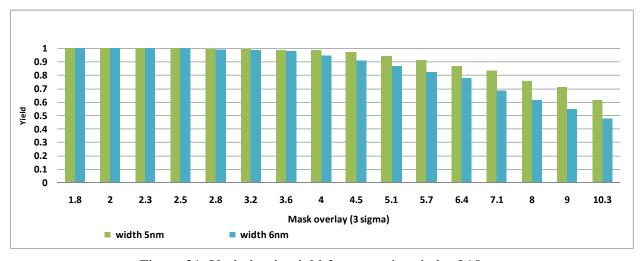

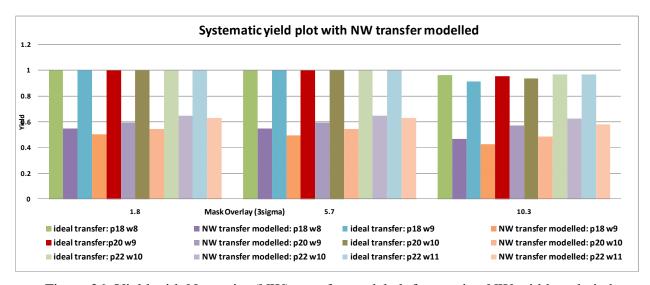

| 26 Yield with Nanowire (NW) transfer modeled; for varying NW width and pitch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 45       |

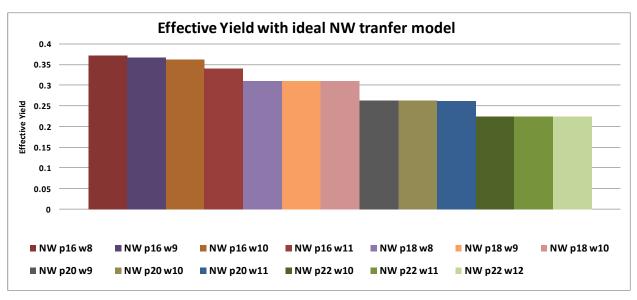

| 27 Effective yield plots for varying pitch and width                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 46       |

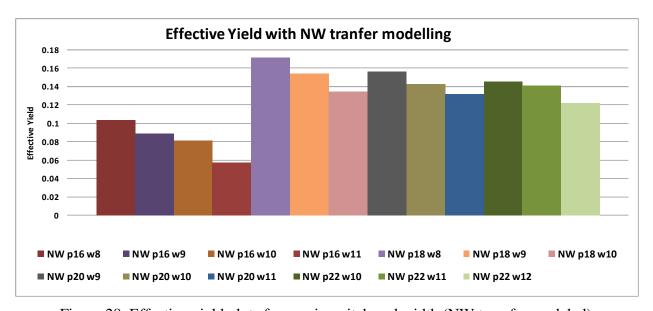

| 28 Effective yield plots for varying pitch and width (NW transfer modeled)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 46       |

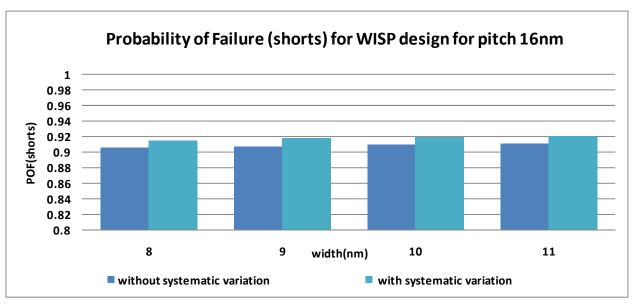

| 29 POF plot for pitch 16nm; width 8, 9nm (with and without systematic variation)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

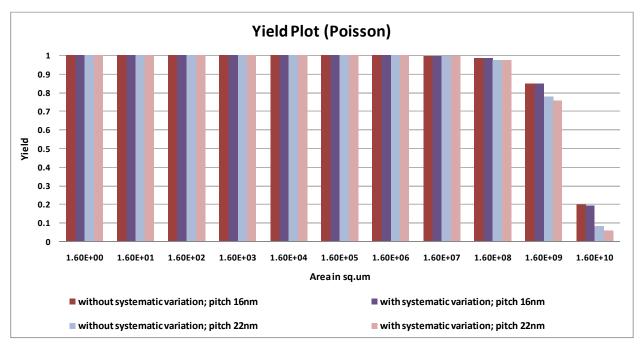

| 30 Particulate Limited Yield loss using Poisson model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 49       |

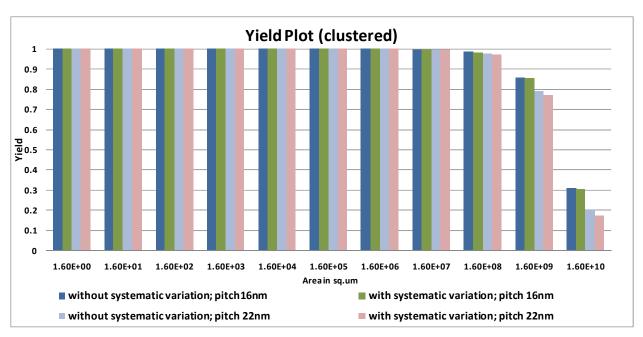

| 31 Particulate Limited Yield loss using Clustered model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

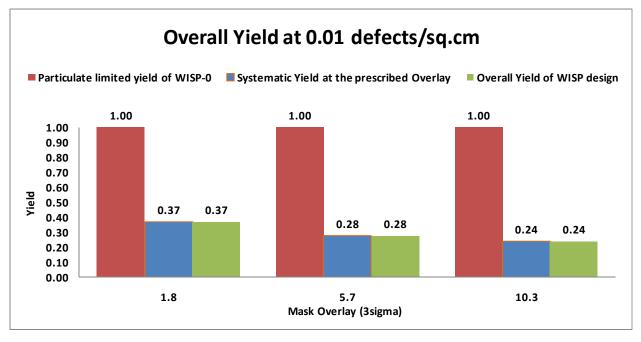

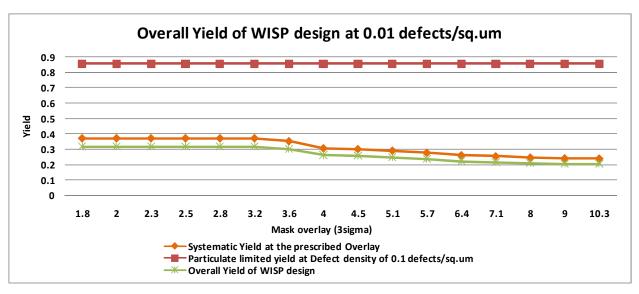

| 32 Overall Yield estimation of wisp design at pitch16nm; width 8nm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |