## 基于 FPGA 的连通域标记设计与实现

谭许彬 谢宜壮 陈 禾 边明明 (北京理工大学雷达技术研究所北京100081)

摘 要:提出了一种基于 FPGA 的连通域标记电路设计方案。该方案不仅满足了实时、高精度等要求,还特别增加了虚警剔除的功能。该硬件设计方案采用单次逐像素扫描法,该法通过对图像进行一次逐像素扫描,将标记与参数并行处理,最后根据统计出来的连通域及参数信息实现虚警剔除。相比较其它的硬件实现方案,该设计方案具有显著优势,通过优化标记与参数处理,该方案更适合硬件的并行处理特性;去除了第二次逐像素扫描,使得处理时间变短,资源占用率变小。仿真结果表明:若图像大小为  $M \times N$ ,临时标记区域上限为 L,则标记完一幅图像总时钟周期为( $M \times N \times 2 + L \times 4$ ).该方案已在单片 Virtex-II 系列 FPGA 中实现,并作为关键电路应用于舰船图像检测系统中。

关键词:连通域标记; FPGA; 单次逐像素扫描法; 虚警剔除

中图分类号: TP391 文献标识码: A 文章编号: 1003-0530(2011)11-1729-05

# Design and Implementation of the connected component labeling based on FPGA

TAN Xu-bin XIE Yi-zhuang CHEN He BIAN Ming-ming (Beijing Institute of Technology University, Institute of Radar Technology, Beijing 100081)

Abstract: A hardware scheme for connected component labeling circuit based on FPGA is proposed in this paper. It not only meets the real-time, high accuracy requirements, but also increases a particular false alarm removing section. A pixel-by-pixel single scanning method is applied in this program, this method carries out a pixel by pixel image scanning, and while achieving the labels processing parallels in time to the parameters processing section, then according to the statistical information, removed false-alarm regions. Compared to other hardware implementation project, this scheme has its significant advantages, by optimizing labels and parameters organizing section, it is more in line with parallel processing features of hardware; time and memory consumption are reduced through removing the second scan process. Simulation results demonstrates that the total cycle of clocks for labeling a image is  $(M \times N \times 2 + L \times 4)$ , if the image size is  $M \times N$ , the maximum temporary regional labeling is L. This method is implemented on a single VIRTEX- II series FP-GA and has been applied to a ship detection system as a critical module.

Key words: connected component labeling; FPGA; a pixel-by-pixel single scanning; false alarm removing

## 1 引言

在实际应用中,基于全色卫星遥感图像的舰船目标检测系统要求能准确、高时效地实现舰船检测。作为其中的关键步骤之一,设计快速高效的连通域标记电路已成为制约整个系统检测速度与精度的瓶颈。连通域标记的目的是在获得表征目标候选区域的二值图后,以某种算法方式标记出其中的四连通二值区域,供后续步骤进一步分析、提取目标信息。

针对以上瓶颈,本文结合 FPGA 的特性提出一种 单次逐像素扫描的连通域标记方法,并且基于 Xilinx 公司的 Virtex- II 系列 FPGA 实现了该方法电路的设计,与其它算法相比有如下三个突出优点:(1)相比文献 [1]提出的一次扫描法,本文方法不存在大量重复扫描,算法更规整,适合完全硬件实现。(2)相比海量遥感分类图连通域标记方法[2],本文方法可直接对 1k×1k 的图像进行标记,不需要进行图像的分块标记,增强了连续大规模数据的处理能力,避免了由于分块处理所需的后续目标候选区域合并操作。(3)相比文献 [3]提出的一种适合硬件实现的多值图像连通域的标记算法,及文献[4]的基于 ASIC 设计的多值图像连通域标记方法,本文方法将等价表操作与参数统计模块

合并优化,使得电路控制逻辑大为简化,同时缩减了约50%的计算时间。

## 2 算法原理

单次次逐像素扫描法主要通过先对图像进行一次 从左到右,从上到下的扫描即进行图像标记,同时将生 成的新的临时标记、等价标记、参数存储起来同时进行 初步整理;等到扫描完毕即图像标记结束后,对临时标 记与参数信息进行整理替换和虚警剔除,完成后,将符 合要求的标记和参数信息输出,省去了再次标记的过 程。算法可分为三个环节:图像标记、临时标记及参 数整理替换、虚警剔除。

#### 1. 图像标记

这一部分完成每个像素的临时标记以及临时标记 等价关系的收集和初次整理。在进行逐像素扫描图像 的过程中,判断灰度值不为零的当前点与其左、上点的 灰度值关系,赋予新的临时标记或记录等价关系。

#### 2. 标记及参数处理

临时标记与参数存储在一维数组 G 中,其中,数组的下标为临时标记值,相应单元的高位内容指示该临时标记的等价关系,低位内容指示该临时标记区域的参数信息,例如:  $G(l_2) = l_1$ ,表示临时标记  $l_1 = l_2$  等价,即标记为  $l_1 = l_2$  的区域连通,此时更新参数信息。为了便于组织和查找,等价表按照  $l_1 \ge l_2$  的原则组织。

标记及参数处理主要有三个步骤:(1)图像标记过程中,当出现新的临时标记时,则在初始化等价表的同时存储了所需的信息;当出现新的等价关系时,在记录等价关系的同时替换了所需的参数信息。(2)图像标记完成后,从地址1开始对整个数组的扫描一遍,对每个具有等价关系的临时标记追踪[9]一遍,则整个数组中具有等价关系的标记均对应相同的最小标记,均对应相同的最佳参数值。(3)再次对整个数组的扫描一遍,对临时标记重新赋值后,最终标记的个数等于图像中连通区域的个数。

#### 3. 虚警剔除

在替换的过程中,控制进行恒虚警剔除,根据读取替换过程中已经获得每个连通区域的参数信息,进行恒虚警剔除(其中恒虚警剔除所选用门限值为所需检测的目标舰船实际大小范围和卫星图片的比例确定),剔除过大过小面积,输出最终符合条件的标记区域的编号和参数信息。

## 3 连通域标记的电路实现

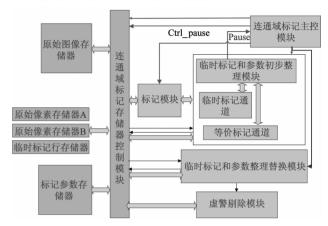

图1是星载大视场海面舰船检测系统中连通域标记电路的硬件实现总体架构图。其中,原始图像存储

器大小为1k×128×8bit,可以存储1幅1k×1k的二值图像数据;原始像素存储器A和B大小为1k×1bit,用来做标记过程时乒乓存储每一行的图像数据,标记参数存储器数据大小为4k×52bit,其中4k代表原始图像中可能的最大标记区域为4096个,52bit中高12位为等价表存储区域,低40位为参数存储区域。

图 1 连通域标记电路总体架构图

Fig. 1 Overall structure of connected component labeling circuit

连通域标记电路工作流程为:

- 1. 检测到存完一幅图像后,主控电路给出启动信号,启动连通域标记操作开始。

- 2. 开始后,由主控电路控制连通域标记存储器控制电路将数据从原始图像存储器中乒乓写人原始像素存储器 A 和 B,同时启动标记和临时标记和参数整理电路,并将临时标记和参数写人标记参数存储器。

- 3. 步骤 2 结束后,由主控电路控制连通域标记存储器控制模块从标记参数存储器中将数据顺序读出,同时启动临时标记及参数整理替换的整理电路,整理结果写回标记参数存储器。

- 4. 步骤 3 结束后,启动替换电路,同时启动虚警剔除电路。

- 5. 步骤 4 结束,则读入下一幅图。

上述硬件电路中,标记模块、临时标记和参数初步整理模块、临时标记和参数整理替换模块是其中的关键模块,下面详细说明等等。

## 4 关键模块设计

#### 4.1 标记模块

标记模块采用3个行存储器进行操作,其中,原始像素存储器A和原始图像存储器B作为乒乓进入的图像像素灰度存储器,临时标记行存储器则用于存储对应像素点的临时标记。在1024×1024×2个cycle后,标记模块操作可以结束。考虑到四连通标记的算法原理,对于1k

×1k 的二值图,进行全图标记主要有三种情况:

#### 1. 第1行

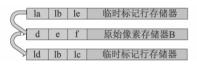

对二值图的第1行进行标记时,则只需判断其左点的临时标记值和当前点的灰度值,如图2所示:

a

b

c

原始像素存储器A

la

lb

le

临时标记行存储器

图 2

第 1 行标记示意图

Fig. 2 Labeled diagram of line 1

若要标记 b 点,则只需知道 a 点的临时标记值和 b 点的灰度值,用 1 个 12bit 的寄存器 label\_reg 将每次读出的像素点的临时标记存入,则同时读取 label\_reg 和原始像素存储器 A 相比较后就可得到 b 点的临时标记值 lbit,将 lbit 同时写入 label\_reg 和临时标记存储器的对应位置,则标记第一行需要 1024×2 个 cycle。

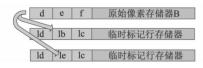

#### 2. 第1列

对二值图的第一列进行标记时,只需判断其上点的值和当前点的灰度值,如图 3 所示:

图 3 第 1 列标记示意图

Fig. 3 Labeled diagram of line 2

同理,则标记第1列需要1024×2个cycle。

3. 第2~1024 行、第2~1024 列

对二值图的第2~1024 行、第2~1024 列进行标记时,需判断其左点、上点的值、当前点的灰度值,如图 4 所示:

图 4 第 2 ~ 1024 行、第 2 ~ 1024 列标记示意图 Fig. 4 Labeled diagram of line 2 ~ 1024, column 2 ~ 1024

同理,标记1个像素需要2个cycle。

#### 4.2 临时标记和参数初步整理模块

临时标记和参数初步整理电路主要有两个功能:

- 1. 对新的临时标记和等价关系的临时标记进行 整理[6][10];

- 2. 记录整理每个临时标记区域的 x、y 坐标的最值。

由图 1 可知,此电路接受主控电路的控制、接收从标记电路来的新的临时标记和等价标记,与标记电路同步进行。在电路设计时,令临时标记和参数初步整理模块的优先级大于标记模块,即若缓存从标记模块

来的新的临时标记和等价标记的通道满,若输出 pause 信号给主控模块,控制标记暂停,等处理完后,恢复标记工作。

#### 4.3 临时标记及参数整理替换模块

临时标记及参数整理替换电路完成标记电路后的 标记及参数整理过程,其主要功能如下:

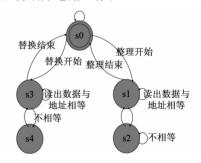

#### 1. 整理讨程

如图 5 所示为 s0->s1->s2 过程,从标记存储器地址 1 开始读取高 12bit 数据,若读出的数据与地址相等,转而处理下一单元;否则,记录此单元的地址,以数据作为地址,再次读取标记参数存储器,此时读出的数据与地址相等,以读出数据更新前面保存地址的单元,转而处理下一单元。重复上述过程直到处理结束。

### 2. 替换过程

如图 5 所示为 s0->s3->s4 过程,此时整理电路已停止工作。从标记存储器地址 1 开始读取高 12bit 数据,如果读出的数据与地址相等,则以最终标记值写入该单元,同时最终标记值加 1;如果读出的数据与地址不相等,则以数据为地址再次读取,并将读出的数据写入原单元中。重复上述过程直到处理结束。其中替换过程控制虚警剔除电路工作。

图 5 整理替换模块状态机流程

Fig. 5 Flow chart of finish and replace module

如图 5,当标记电路与其对应初步整理电路完成之后,主控电路给一个 start 信号启动 s0->s1->s2 过程,当此整理过程结束之后,主控电路给出一个 start 信号启动 s0->s3->s4 过程,替换过程完成后,连通域标记电路输出 done 信号告知主控电路可以进行下一幅图像的标记操作。

## 5 仿真结果

#### 1. 资源耗损

连通域标记电路在单片 Virtex- II 系列 FPGA 中实现,其中,根据置信区间确定可能的连通区域最大有4096 个。

#### 表 1 FPGA 资源耗费列表

Tab. 1 FPGA resource consumption list

| 名称        | 类型    | 资源耗费    |

|-----------|-------|---------|

| 原始图像存储器   | SRAM  | 128KB   |

| 标记参数存储器   | SRAM  | 26KB    |

| 原始像素存储器 A | SRAM  | 1 KB    |

| 原始像素存储器 B | SRAM  | 1 KB    |

| 临时标记存储器   | SRAM  | 12KB    |

| 临时标记通道    | FIFO  | 0.047KB |

| 等价标记通道    | FIFO  | 0.094KB |

| 逻辑资源      | SLICE | 432 个   |

表 2 存储器内数据组织结构

Tab. 2 Memory data structure

| <br>名称  | 数据位     | 作用     |

|---------|---------|--------|

| 标记参数存储器 | 51 ~40  | 标记值    |

|         | 39 ~ 30 | Xmax   |

|         | 29 ~ 20 | Xmin   |

|         | 19 ~ 10 | Ymax   |

|         | 9 ~ 0   | Ymin   |

| 等价标记通道  | 24 ~ 12 | 大的临时标记 |

|         | 11 ~0   | 小的临时标记 |

#### 2. 时间耗费

此电路对于大小为 M×N,连通区域最大上限为 L 的二值图像,处理频率为f时,所需时间为 $t=(M\times N\times$  $2+L\times4$ )×f。参考其它实现方法[3][4]中,对于同样的 图像,忽略等价表整理的时间,实现的总时钟周期数为  $(M \times N \times 4)$ :若本文算法同样忽略等价表整理的时间, 则标记完一幅图像的时间仅为参考方法的一半。

#### 3. 连通域标记系统处理结果

连通域标记电路对二值图像的处理结果,如图 6 所示,为未处理的原始二值图像。

图 6 待处理二值图像

Fig. 6 Binary image to be processed

如图 7 所示, 为不使用虚警剔除时连通域标记电 路对二值图像进行的处理,此时从细节图可以看出,利 用统计出来的 x,v 坐标的最值在每个标记出来的区域 都画了一个方框。

图 7 标记图像 Fig. 7 Labeled image

如图 8 所示,为虚警剔除后的标记图像,此时从细 节图可以看出,只有符合条件的标记区域才被方框框 住,即去除了其他区域的信息。

Fig. 8 Labeled image after removing false alarm

对于图6至图8进行标记的整个过程发现了21个 临时标记区域,经过虚警剔除后剩下两个有效区域,时 钟周期为1024×1024×2 + 21×4 个 cycle,以60Mhz 的频 率进行处理,时间为34ms。

## 结论

本文通过一种单次逐像素扫描连通域标记法,实 现通过对 1k×1k 的大视场海面全息图像扫描一次后得 到所需参数信息。经过实验结果证明,在标记过程中, 该电路采用存储器 A 和 B 进行乒乓操作,可以快速流 畅的标记完图像;通过将所需的参数和临时标记合并 存储,使得对图像扫描一次即可达到标记目的和进行 虚警剔除,不仅提高了其在 FPGA 中实现的规范性,还 降低了控制的复杂性和时间的耗费。

#### 参考文献

- [1] Martin-Herrero. Hybrid object labeling in digital images. [J]. Machine Vision and Applications. 2007, 18(1):1-15.

- [2] 马江林,赵忠明,孟榆,彭铃.海量遥感分类图连通域 标记方法.[J]. 计算机工程,2008,第34卷(第1期):

1-3 页.

MA Jiang-lin, ZHAO Zhong-ming, MENG Yu, PENG Ling. Connected Component Labelling for Massive Remote Sensing. Classification Image. [J]. Computer Engineering. January 2008,34(1):1-3. (in Chinese)

- [3] 桑红石,傅勇,张天序,刘云生. 一种适合硬件实现的 多值图像连通域的标记算法.[J]. 华中科技大学学报, 2005,第33卷(第9期):1-4页.

- SANG Hong-shi, Fu Yong, Zhang Tian-xu, Liu Yunsheng. A connected components labeling algorithm for multi-value image that suitable for realization in VLSI. [J]. Journal of Huazhong University of Science and Technology (Natural Science Edition). Sep. 2005. 33(9):1-4. (in Chinese)

- [4] 桑红石,赵慧,尚社. 多值图像连通域标记 ASIC 设计. [J]. 小型微型计算机系统,2008,第 29 卷(第 1 期): 1-4 页.

- SANG Hong-shi, ZHAO Hui, SANG She. Architecture Design of Asic Used for Connected Components Labeling of Multi-value Image. [J]. Journal of Chinese Computer Systems. 2008, 29 (1):1-4. (in Chinese)

- [5] SUZUKI K, HORIBA I, SUGIE N. Linear time connected component labeling based on sequential local operations.

[J]. Computer Vision and Image Understanding. 2003, 89

(1):1-23.

- [6] 冈萨雷斯. 数字图像处理[M]. 第二版. 电子工业出版 社,2005:307-315页.

Rafael C. Gonzalez. Digital Image Processing[M]. Sec-

ond Edition. Publishing House of Electronics Industry. 2005; 307-315. (in Chinese)

#### 作者简介

谭许彬(1987-),女。硕士研究生,北京理工大学雷达技术研究所。主要研究方向:信号与信息处理、目标探测与识别。E-mail;20905202@bit.edu.cn

谢宜壮(1980-),男。讲师,博士,北京理工大学雷达技术研究所。主要研究 方向:高速实时信号处理。

E-mail:xyz551\_bit@bit.edu.cn

陈 禾(1970-),女。副教授,博士, 北京理工大学雷达技术研究所,博士生导师。主要研究方向:信号处理、信息系统 小型化设计。E-mail;chehe@bit.edu.cn

边明明(1985-), 男。博士研究生, 北京理工大学雷达技术研究所。主要研究方向: 信号与信息处理、目标探测与识别。E-mail; bmm1429@ bit. edu. cn