Vol.28 No.27 Sep. 25, 2008 ©2008 Chin.Soc.for Elec.Eng.

35

文章编号: 0258-8013 (2008) 27-0035-07

中图分类号: TK 228 文献标志码: A

学科分类号: 470.40

# 高压大功率三电平逆变器的 SPWM 数字化技术研究

刘健, 尹项根, 张哲, 熊卿

(电力安全与高效湖北省重点实验室(华中科技大学), 湖北省 武汉市 430074)

# Study of SPWM Digital Technologies for High-voltage High-power Three-level NPC Inverter

LIU Jian, YIN Xiang-gen, ZHANG Zhe, XIONG Qing

(Hubei Electric Power Security and High Efficiency Key Lab(Huazhong University of Science and Technology), Wuhan 430074, Hubei Privince, China)

ABSTRACT: With the application of digital sinusoidal pulse width modulation(SPWM)control technologies, the precision, responding time, security and stability of the pulse width gating signals can be improved conspicuously. In this paper, the digital theory of triangular carrier and sinusoidal modulation wave generation, PWM duty cycle calculation, switching states configuration and gating signals fault diagnosis were studied with the combination of characteristics of high-voltage high-power three-level neutral point clamped (NPC) inverter. At the same time, the simplified calculation method, all round dead state configuration, universal over-modulation principle and fast output block technology of fault PWM signals have been put forward. At last, the DSP+FPGA+CPLD based new digital implementation circuit of the control system is presented. The simulation and experimental results are given to verify the correctness, feasibility of the digitization assumption.

**KEY WORDS:** three-level neutral-point-clamped inverter; sinusoidal pulse width modulation; asymmetrical regular sampling; digital control theory

摘要:数字化的正弦脉宽调制(digital sinusoidal pulse width modulation, SPWM),能够提高脉宽控制信号输出精度,缩短控制响应时间,增加系统安全稳定性。结合高压大功率中性点箝位(neutral point clamped, NPC)三电平逆变电路的特点,对其 SPWM 数字化过程中三角载波形成、正弦调制波发生、器件开关时间计算、开关状态组合配置以及脉宽信号故障诊断的数字化原理进行了研究。提出了简化的开关时间计算方法、完善的死区设置、通用的超调制原则以及故障信号高速闭锁的实现方法。最后利用 DSP+FPGA+CPLD 的新型结构实现了三电平逆变器的高性能数字化控制,仿真和试验结果证明了该文数字化构想的正确性和可行性。

关键词:中性点箝位三电平逆变器;正弦脉宽调制;不对称

规则采样:数字化控制理论

# 0 引言

随着电力电子技术以及大功率、全控型半导体 开关器件的不断发展,各种高压大功率变换器的应 用越来越广泛<sup>[1-2]</sup>,拓扑结构也由传统的两电平向着 多电平、多重化的方向发展。中性点箝位三电平拓 扑结构便是其中一种<sup>[3]</sup>,其多电平脉宽调制技术的 原理更复杂<sup>[4-5]</sup>、影响调制性能的因数更多<sup>[6-7]</sup>、系 统安全稳定性要求更高<sup>[8]</sup>、实现方法也更加多样<sup>[9]</sup>, 主要的特点和关键问题包括:

- 1) 高压大功率场合开关频率低(1000 Hz以下), 死区时间与最小脉冲宽度设置较大(几十μs),自然 采样与规则采样方法、同步调制与异步调制之间的 性能差距已不明显,而减小输出电压谐波,提高直 流母线电压利用率成为重点。

- 2) 当要求逆变器输出电压的频率、相位、幅值 均快速(ms 等级)且大范围变化时,优化的调制算法 和实现技术成为关键。

- 3)多载波技术的引入,使主电路脉宽控制信号组合和约束条件增加,系统死区设置更复杂;同时,局部短路现象的存在,使得合理的死区设置必须加以采用。

- 4) 高压大功率场合对脉冲触发的安全稳定性 要求远高于低压小功率场合。完善的故障识别和容 错处理非常必要。

解决好以上问题是三电平逆变器数字化技术 理论研究的几个重点。文献[10-11]对低压小功率场 合两电平逆变器的脉宽调制的数字化理论进行了研 究,并利用现场可编程门阵列(field programmable gate array,FPGA)芯片加以实现。文献[12-14]分别对多种三电平脉宽调制技术进行了研究,其中文献[13-14]还利用集成 PWM 功能的专用数字信号处理(DSP)芯片对设计方案进行了实现。但以上方法尚不能完全满足系统功能复杂、计算量大、稳定性要求高的高压大功率场合的要求。本文将针对上述几个理论问题,结合当前技术现状,对三电平逆变电路SPWM 数字化技术的理论进行研究,并采用DSP+FPGA+CPLD的新型组合结构加以实现。

# 1 三电平逆变器拓扑结构及其 2 种 SPWM 采样法的原理和性能比较

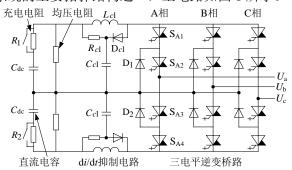

中性点箝位三电平拓扑结构在文献[3]中有详细介绍,该拓扑结构直流母线电压由多个开关器件共同承担,逆变系统具有输出谐波含量低、功率大、du/dt变化率小等优点,目前已成为高压大功率变换系统的主要拓扑结构之一,主电路如图 1 所示。

图 1 三电平逆变器主电路拓扑结构 Fig. 1 Main circuit of three-level NPC inverter

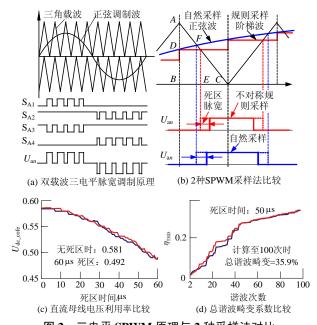

三电平逆变桥路的正弦脉宽调制(SPWM)方法有很多,自然采样法和不对称规则采样法是其中2种。图 2(a)给出了一相桥臂 SPWM 的调制原理,根据调制方法控制 A 相桥臂 4 个开关器件,可以将 A 相输出端接至直流母线的正极、负极和中性点位置从而输出三种电平状态。图 2(b)中给出了正弦调制波大于零时的不对称规则采样和自然采样的原理图。图 2(c)、(d)是不对称规则采样与自然采样之间直流母线电压利用率和总谐波畸变系数的对比分析(输出频率为 50 Hz,开关频率为 900 Hz,幅值调制比为 0.9)。

其中直流母线电压利用率 $U_{dc\_cofe}$ 和总谐波畸变系数 $THD(\eta_{THD})$ 计算公式为

$$\begin{cases}

U_{\text{dc\_cofe}} = U_{1} / U_{\text{dc}} \\

\eta_{\text{THD}} = \frac{1}{U_{1}} \left( \sum_{n=2,3,4,\dots}^{\infty} U_{n}^{2} \right)^{1/2}

\end{cases} \tag{1}$$

式中:  $U_{dc}$ 为直流母线电压;  $U_1$ 和 $U_n$ (n=2,3,4...)为逆变器线电压基波和各次谐波的有效值。

图 2 三电平 SPWM 原理与 2 种采样法对比 Fig. 2 Multi-level SPWM principle and performance comparison of the two sampling method

由图 2(c)、(d)可以看到,2种方法在直流母线电压利用率上基本相同,但受死区时间的影响较大。规则采样法在 40 次以前的总谐波含量略大于自然采样法,随着谐波分析次数的提高,2 者之间已经趋向相等。可见在高压大功率场合2种实现方法的性能的差距已不明显。但不对称规则采样在计算量、对称死区设置、超调制实现上均优于自然采样法。因此,研究不对称规则采样 SPWM 的数字化实现方法具有重要的理论意义和应用价值,下面文章将对其原理与算法、死区设置和超调制等问题进行研究与分析。

# 2 不对称规则采样 SPWM 数字化理论研究

# 2.1 基本算法与开关状态

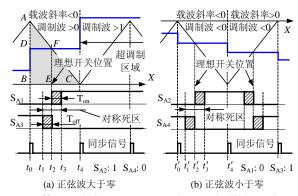

图 3 为基于双载波、双边对称死区的三电平不对称规则采样数字化算法示意图。在数字化过程中,核心内容是开关器件的开通与关断时间计算以及开关状态选择。首先对图 3(a)中调制波大于零,载波斜率小于零区间的开关时间计算进行分析,根据图 2(a)中的调制原理,此时 $S_{A2}$ 器件一直开通, $S_{A4}$ 一直保持关断,因此,该区间内只需对 $S_{A1}$ 和 $S_{A3}$ 的开通关断时间进行计算。令变量: $S_{A1_ON}$ , $S_{A3_OFF}$ 分别为 2 个器件加入死区处理后的最终开通关断时间,则有

图 3 基于双载波的三电平不对称规则采样算法示意图 Fig. 3 Double carrier wave based asymmetrical regular sampling SPWM algorithm of three-level NPC inverter

$$\begin{cases} S_{\text{Al\_ON}} = (t_4 - t_2) - (1/2)P_{\text{WM\_DT}} \\ S_{\text{Al\_OFF}} = P_{\text{WM\_TM}} - S_{\text{Al\_ON}} - P_{\text{WM\_DT}} \\ S_{\text{A3\_ON}} = (t_2 - t_0) - (1/2)P_{\text{WM\_DT}} \\ S_{\text{A3\_OFF}} = P_{\text{WM\_TM}} - S_{\text{A3\_ON}} - P_{\text{WM\_DT}} \end{cases}$$

(2)

式中:  $P_{\text{WM\_DT}}$ 为死区时间;  $P_{\text{WM\_TM}}$ 为半个载波周期时间(即BC段时间);  $t_4$ – $t_2$ 段为 $S_{A1}$ 的理论开通时间;  $t_2$ – $t_0$ 段为 $S_{A3}$ 的理论开通时间;

根据图 3 (a)中阴影部分的 2 个相似三角型 *ABC* 与 *ADF* 有如下关系。

$$\frac{|DF|}{|BC|} = \frac{|AD|}{|AB|} \Rightarrow \frac{|BC - CE|}{|BC|} = \frac{|AB - DB|}{|AB|}$$

(3)

令三角载波幅值为 AB=1,将图 3(a)中变量代入式(3)可得

$$\frac{P_{\text{WM\_TM}} - CE}{P_{\text{WM\_TM}}} = \frac{1 - P_{\text{WM\_M}} \times \sin(\omega t_0 + \varphi)}{1}$$

(4)

式(4)中, $P_{\text{WM\_M}}$ 为幅值调制比; $t_0$ 时刻正弦波 采样值为 $\sin(\omega t_0 + \varphi)$ 。根据式(4)可以计算出 $t_4 - t_2$ (即CE段时间长度)与 $t_2 - t_0$ (即EB段时间长度)的数值分别为

$$t_4 - t_2 = P_{\text{WM TM}} \times P_{\text{WM M}} \times \sin(\omega t_0 + \varphi) \tag{5}$$

$$t_2 - t_0 = P_{\text{WM TM}} - (t_4 - t_2) \tag{6}$$

将式(5)、(6)带入式(2)即可得到S<sub>A1</sub>与S<sub>A3</sub>器件的 开通关断时间,以上计算在同步信号产生时完成(即 三角波顶点和底点)。由式(5)可以看出采用不对称规 则采样法后,将开关时间计算中乘法次数降低至 2 个。

根据图 2(a)三电平调制原理可以总结出 1 个完整调制波周期之内的全部开关状态组合,如表 1 所示。表中'1'表示开通;'0'表示关断。" $S_1$ "表示输出正电平状态," $S_0$ "表示输出零电平状态," $S_{-1}$ "表示输出负电平状态。" $S_{d+}$ "表示正死区状

态,"S<sub>d</sub>"表示负死区状态。表 1 中各个开关状态 开关时间计算均与前面推导过程类似。

表 1 A 相桥臂开关状态列表 Tab. 1 Switch states of A phase bridge arm

| 开关       | 正弦调制波>0 |           |       |       |             |       | 正弦调制波<0  |         |       |       |          |          |

|----------|---------|-----------|-------|-------|-------------|-------|----------|---------|-------|-------|----------|----------|

| 状态       | 载测      | 支斜率       | ~<0   | 载池    | <b>安斜</b> 3 | 率>0   | 载测       | 支斜.     | 率<0   | 载波    | 斜        | 率>0      |

| $S_{A1}$ | 0       | 0         | 1     | 1     | 0           | 0     | 0        | 0       | 0     | 0     | 0        | 0        |

| $S_{A2}$ | 1       | 1         | 1     | 1     | 1           | 1     | 0        | 0       | 1     | 1     | 0        | 0        |

| $S_{A3}$ | 1       | 0         | 0     | 0     | 0           | 1     | 1        | 1       | 1     | 1     | 1        | 1        |

| $S_{A4}$ | 0       | 0         | 0     | 0     | 0           | 0     | 1        | 0       | 0     | 0     | 0        | 1        |

| State    | $S_0$   | $S_{d^+}$ | $S_1$ | $S_1$ | $S_{d^+}$   | $S_0$ | $S_{-1}$ | $S_{d}$ | $S_0$ | $S_0$ | $S_{d-}$ | $S_{-1}$ |

#### 2.2 死区设置

在高压大功率场合,由于系统电压等级高、电流大,直流环节 di/dt 抑制电路中电感续流作用的存在,以及电路中二极管反向恢复过程的存在,使得三电平逆变电路的死区状态设置多样,约束条件复杂。因此在数字化实现过程中,除了正常情况下的死区设置外,还需要考虑各种特殊情况下的处理。

# 1) 常规死区设置。

三电平每一相桥臂的器件在开关过程中需要插入较长的死区时间,以避免桥臂发生短路的现象。 图 3 和表 1 给出了正常情况下的死区设置情况,在 三角载波和正弦调制波没有发生突变的区域,提前 计算好开关时间后,直接按照表 1 规定,设置图 3 中" $T_{on}$ "和" $T_{off}$ "(图中阴影部分)所示的延时开通 和提前关断的死区即可。

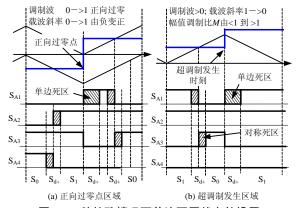

#### 2)特殊区域死区设置。

为了达到更优良的输出波形,系统一般都要求 采用双边对称死区设置。但是由于三电平本身死区 状态多,加之数字化处理后在正弦波过零点区域, 超调制发生和返回区域内计算数据和程序会发生突 然的变化和跳转,此时开关器件将同时进行开、关 操作,导致桥臂发生短路现象。因此在以上区域中 必须进行特殊的处理。图 4 给出了 2 种特殊情况下

图 4 2 种特殊情况下单边死区状态的设置

Fig. 4 Unilateral dead-state setting under special condition

需要设置单边死区的示意图。表 2 列出了调制过程中所有需要进行单边死区设置的情况。当 A 相脉宽调制过程满足表中所示的情况时,各开关器件都必须加入独立的死区,以保证开关器件不会因短路而损坏(B、C 相类似)。

表 2 A 相桥臂所有特殊情况列表

Tab. 2 Unilateral dead-state configuration list of phase A

| 特殊区域                  | 调制波过零点 |      |  | 超调制发生与返回点 |      |                          |  |  |

|-----------------------|--------|------|--|-----------|------|--------------------------|--|--|

| 死区设置                  | 调制波    | 载波斜率 |  | 调制波       | 载波斜率 | 幅值调制比                    |  |  |

| S <sub>A1</sub> U-D-S | 0->1   | 0->1 |  | 1         | 1->0 | m<1->m>1                 |  |  |

| $S_{A2}$ U-D-S        | 0->1   | 1->0 |  | 0         | 0->1 | m>1>m<1                  |  |  |

| $S_{A3}$ U-D-S        | 1->0   | 0->1 |  | 1         | 1->0 | <i>m</i> >1> <i>m</i> <1 |  |  |

| S <sub>A4</sub> U-D-S | 1->0   | 1->0 |  | 0         | 0->1 | <i>m</i> <1> <i>m</i> >1 |  |  |

注: 1-调制波大于零和载波斜率大于零; 0-调制波小于零和载波斜率小于零; ->-发生过渡情况; U-D-S-器件需要添加单边死区。

# 3) 避免局部短路现象发生的死区设置。

在高压大功率场合,箝位二极管和 di/dr 抑制回路的二极管存在反向恢复特性是导致主电路局部短路的主要原因。由于二极管反向恢复过程中反向恢复电流与反向电流变化率 di/dr 成正比(5SDF02D6004大功率快恢复二极管,额定工况下该比值约为1.25)。而在高压大功率开关场合电流变化率 di/dr数值很大,因此器件在反向恢复过程中的导通电流幅值也将成比例增大。

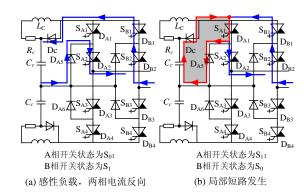

以感性负载为例,对A,B两相行分析。当A,B两相输出电压均为正时,存在A相电流为正,B相电流为负的区域,如图 5(a)所示。当A相的状态为"S<sub>0</sub>",B相的状态为"S<sub>1</sub>"时,A相负载电流由中性点流出,B相负载电流经过开关器件的反向续流二极管流入直流正母线。如果按照常规脉宽调制的规则,当A相的开关状态将由"S<sub>0</sub>"转变到"S<sub>1</sub>",此时,抑制回路和箝位电路的二极管D<sub>c</sub>,D<sub>AS</sub>将会同时进入反向恢复过程,会出现图 5(b)中的阴影区域所示的局部短路现象,在该回路中电流变化率为 $di/dt = U_{dc} \times \Delta t/(2L)$  (7)

式中:  $U_{dc}$ 为直流母线电压; L为线路电感。

由于 IGCT 开通后本身电感值以及线路杂散电感数值都非常小(一般只有几十个 nH), Δt 时间一般为几个μs, 因此电流变化率 di/dt 数值极大(可达到数 kA/μs), 由此导致二极管的反向恢复电流幅值也成比例增大。这将直接影响到变换系统的安全稳定性, 因此二极管反向恢复过程中的死区设置必须考虑在内。

为避免局部短路现象发生,一种方法是在数字 化过程中采取软件控制的办法,即当A桥臂的控制 状态发生如图 5 所示的变化时,对A相桥臂S<sub>A2</sub>开关器件进行独立控制,让其提前关断,使di/dt抑制回路的二极管与箝位二极管不会出现同时进入反向截止状态,从而避免局部短路现象的发生。表 3 列出了所有需要进行独立控制的开关器件和条件,只要系统负载以及电压、电流满足表 3 中情况,对应的开关器件均需要进行附加控制。

图 5 局部短路现象分析

Fig. 5 Typical partial short circuit process

表 3 避免局部短路附加控制条件及器件列表 Tab. 3 Additional control apparatus and condition list

| 器件              | 感性负载                           | 容性负载                           | 器件       | 感性负载                           | 容性负载                           |

|-----------------|--------------------------------|--------------------------------|----------|--------------------------------|--------------------------------|

| c               | $U_{a} > 0, U_{b} > 0$         | $U_{\rm a} > 0, U_{\rm c} > 0$ | c        | $U_a < 0, U_b < 0$             | $U_{\rm a} < 0, U_{\rm c} < 0$ |

| S <sub>A2</sub> | $I_{a} > 0, I_{b} < 0$         | $I_a > 0, I_c < 0$             | $S_{A3}$ | $I_a < 0, I_b > 0$             | $I_a < 0, I_c > 0$             |

| C               | $U_{\rm b} > 0, U_{\rm c} > 0$ | $U_{\rm b} > 0, U_{\rm a} > 0$ | C        | $U_{\rm b} < 0, U_{\rm c} < 0$ | $U_{\rm b} < 0, U_{\rm a} < 0$ |

| $S_{B2}$        | $I_{b}>0,I_{c}<0$              | $I_{b} > 0, I_{a} < 0$         | $S_{B3}$ | $I_{b}<0, I_{c}>0$             | $I_{b} < 0, I_{a} > 0$         |

| $S_{C2}$        | $U_{\rm c} > 0, U_{\rm a} > 0$ | $U_{c}>0, U_{b}>0$             | C        | $U_{\rm c} < 0, U_{\rm a} < 0$ | $U_{\rm c} < 0, U_{\rm b} < 0$ |

|                 | $I_{c}>0, I_{a}<0$             | $I_{c}>0, I_{b}<0$             | $S_{C3}$ | $I_c < 0, I_a > 0$             | $I_{c}<0, I_{b}>0$             |

# 2.3 超调制实现

由图 2(c)可以看到当死区时间为 60 μs 的时候,直流母线电压利用率只有 0.492,无死区的时候利用率也仅为 0.581,这时候采用注入三次谐波或者改变载波形式的方法已经不能完全满足要求,通用的超调制办法必须采用。图 3(a)中给出了正弦波大于零时超调制区域的控制信号状态。在数字化实现过程中,超调制功能实现较容易,只要按照图 3(a)原理和表 4 所规定的要求触发脉冲即可完成。

表 4 超调制脉宽控制信号

Tab. 4 Pulse width control states under over-modulation

| 状 态        | A 相控制信号(B、C 相类似)                         |  |  |  |  |  |  |

|------------|------------------------------------------|--|--|--|--|--|--|

| 正弦波>0, m>1 | $S_{A1}=1; S_{A2}=1; S_{A3}=0; S_{A4}=0$ |  |  |  |  |  |  |

| 正弦波<0, m>1 | $S_{A1}=0; S_{A2}=0; S_{A3}=1; S_{A4}=1$ |  |  |  |  |  |  |

由以上分析可以得出,通过数字化处理以后不对称规则采样 SPWM 具有如下特点:

1) 仅通过相似三角形比例关系即可求得各器件的开通关断时间,避免了自然采样法中迭代求解开关点位置的复杂计算以及脉冲竞争<sup>[15]</sup>等问题。

- 2)每个载波周期(即功率器件开关周期)内可完成两次开关时间的计算和脉宽输出的调整,系统响应速度快、输出电压谐波含量小。

- 3)提前计算得到未来半个载波周期内的开通 关断时间以及各器件开关状态,方便实现双边对称 死区功能以及超调制功能。

# 3 数字化实现

# 3.1 数字化系统的结构

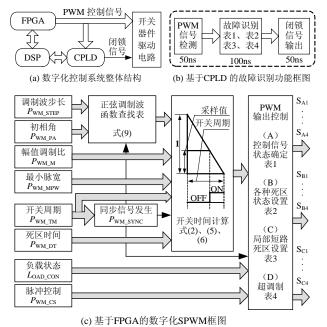

图 6(a)为数字化系统的整体结构,系统由 DSP、FPGA、和 CPLD 共同组成;图 6(b)为基于 FPGA的数字化 SPWM 功能框图;图 6(c)为 CPLD 的内部功能框图。

图 6 基于 DSP+FPGA+CPLD 的数字化控制系统 Fig. 6 DSP+FPGA+CPLD based digital control system

# 3.2 DSP 部分

DSP 将计算和设定的参数通过总线传送给FPGA,使 DSP 能够专注的完成各种高性能的控制与保护算法、系统保护功能、事件与故障报告记录以及通讯等复杂功能,并避免了由于 DSP 软件程序异常造成看门狗动作而中断脉宽输出的问题。

#### 3.3 FPGA 部分

根据图 3 所示原理以及式(2)、(5)、(6)可以看出,全数字化 SPWM 需要有控制信号接收、三角波形成、正弦函数发生、开关时间计算死区插入以及最后的 PWM 输出控制等功能。为满足以上要求,本文设计了基于 FPGA 技术的数字化 SPWM 系统,功能框图如图 6(b)所示。

1) 信号接收。

FPGA 利用缓存先保存 DSP 逐一传送过来的控制参数,当 DSP 返校成功后,将各参数同时投入到 SPWM 算法之中。

### 2) 同步信号发生。

利用一个计数器进行循环累加完成图 3 中所示的同步信号发生,当数值达到半个三角波周期时间所对应的数值,则输出同步信号。开关时间计算,正弦波查表均以该同步信号为基准,公式如下:

$$P_{\text{WM\_TM}} = \frac{f_{\text{CLK}}}{2 \times f_{\text{PWM}}} \tag{8}$$

式中:  $f_{LCK}$ 为FPGA的时钟周期;  $f_{PWM}$ 为功率器件的开关频率。

由式(8)可以确定,当 16 位的 $P_{WM\_TM}=0$ xFFFF时, $f_{PWM}$ 可达到最小值 152.59 Hz。

# 3) 正弦调制波发生。

本文利用FPGA内部的丰富资源,直接采用数字查表的办法实现正弦波的发生。将 0°~90°之间的正弦函数每 0.05°取 1 个点,精度为 12 位,保存在FPGA内部的ROM块中。查表步长 $P_{\text{WM\_STEP}}$ 与初相角 $P_{\text{WM\_PA}}$ 是根据正弦波输出频率和相位由DSP按照如下公式计算得到

$$P_{\text{WM STEP}} = 2\pi f \times \Delta T \times 20 \tag{9}$$

式中: f 为调制波频率;  $\Delta T$  半个三角载波的时间;  $2\pi f \times \Delta T$  为半个三角载波跨越的调制波角度,正弦波查找表每  $0.05^{\circ}$ 一个点,因此在式(9)中最后乘 20,结果即是不同频率下每次递增的地址值。每次同步信号到来后,递增地址累加,得到正弦函数最终地址  $\sin_A Add$ 。计算公式为

$$\begin{cases} \sin_{\text{A}} Add = \sin_{\text{A}} Add + P_{\text{WM\_STEP}} + P_{\text{WM\_PA}} \\ \sin_{\text{A}} Add = \sin_{\text{A}} Add - 360^{\circ}, & \sin_{\text{A}} Add \ge 360^{\circ} \end{cases}$$

(10)

为节省 FPGA 的存储空间,正弦函数只保存了 0°~90°之间的数值,其他角度的函数值在 FPGA 程序中通过对称处理得到。

4) 死区时间。

16 位的死区寄存器 $P_{\text{WM\_DT}}$ 数值由DSP计算,公式为

$$T_{\rm D} = P_{\rm WM-DT} \times t_{\rm CLK} \tag{11}$$

式中:  $T_{\rm D}$ 为死区时间;  $t_{\rm CLK}$ 为FPGA时钟周期(FPGA 采用 20 MHz晶振, $t_{\rm CLK}$ =50 ns),当 $P_{\rm WM\_DT}$ =0x2710 时,死区时间为 50  $\mu$ s。当寄存器 $P_{\rm WM\_DT}$ =0xFFFF时,最大死区时间为

$$T_{\rm D} = (2^{16} - 1) \times t_{\rm CLK} = 65.535 \times 50 \times 10^{-9} = 3.276.75 \ \mu s$$

5) 开关时间计算与 PWM 输出控制。

该部分功能按照式(2)~(6)以及表 1~表 4 的内容 进行计算与控制。并均以同步信号作为启动命令, 每半个载波周期计算更新一次。

# 3.4 CPLD 部分

该部分功能如图 6(b)所示。CPLD实时监测系统PWM控制信号,并判断信号是否满足表 1~4 中的各项要求,若出现异常信号,则闭锁PWM输出,并向DSP传送故障原因。当CPLD晶振为 20 MHz时,故障识别与闭锁信号输出在 200 ns内(包括硬件延时时间)即可实现,完全满足IGCT驱动回路设计的要求(400 ns之内的脉冲信号,IGCT驱动回路认为是干扰信号,并会将其滤除)。

# 4 试验结果与性能分析

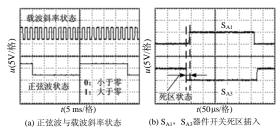

本数字化控制系统已在基于IGCT开关器件串联的 6kV/1000kW高压变频调速系统<sup>[2]</sup>中得到初步应用,图 7(a)~(d)是三电平SPWM数字化处理后,开关频率为 1000 Hz,控制系统输出电压为 50 Hz,死区时间为 20 μs时的几种典型信号的测量波形。从图中可以看出,经过数字化处理后:

- 1)相比模拟电路而言,三角载波、正弦调制波、死区时间设置、脉宽控制信号的精度以及三相对称性均得到了大幅度提高(FPGA 晶振为 20 MHz 时,控制信号精度均为 50 ns)。

- 2) 能够更加安全和方便的实现 SPWM 的超调制功能,进一步降低了系统各器件的电压等级。

- 3)控制系统脉宽信号的响应速度仅与死区时间和最小脉冲宽度相关,半个开关周期内(约 1 ms)即可实现对系统输出频率、相位、幅值的同步调整。完全能够满足各种高性能控制场合的需要。

图 7(e)~(h)是 380 V/7.5 kW电机负载下的试验 波形,可以看出:

1) 合理的死区设置对保护高压大功率逆变器的安全工作具有重要意义,图 7(e)可以看到当死区时间过小时,由于 di/dt 抑制回路放电不充分等原因使得 IGCT 开通过程电流较大。当延长死区时间后,如图 7(f)所示,该不良情况得到了明显改善。

图 7 试验波形 Fig. 7 Experimental results

2) 从图 7(g)电压波形可以看到,主电路 IGCT 器件均能够按照系统的控制信号进行正常的开通和关断。图 7(f)中三电平逆变器的输出电压波形(经过输出 LC 滤波器)的正弦度和三相对称性均达到 GB/T 14549 国家标准。

# 5 结论

本文结合高压大功率中性点箝位三电平逆变器的实际情况,对其正弦脉宽调制数字化技术的理论及其实现技术进行了研究与分析。主要特点与创新包括:

- 1)对三电平 SPWM 数字化理论中的主要算法和存在问题进行了优化与研究,使得数字化求解过程得到简化,并能方便实现各种复杂的死区设置、超调制功能以及系统各变量的快速控制,丰富了多电平脉宽调制理论,并为其实用化奠定了基础。

- 2) DSP+FPGA+CPLD 新结构和技术的采用, 增强了系统运算能力、提高了脉宽输出精度、缩短 了控制响应时间、改善了系统的安全稳定性。

#### 参考文献

[1] Nagel A, Bernet S, Steimer P K, et al. A 24 MVA inverter using IGCT series connection for medium voltage application[C]. Thirty-Sixth IAS

- Annual Meeting, Chicago, USA, 2001.

- [2] Liu Jian, Yin Xianggen, Zhang Zhe, et al. A development of highvoltage and high-power motor drive system[C]. APSCOM 2006, HK, China, 2006.

- [3] Nabae A, Takahash I, Akagi H. A new neutral point clamped PWM inverter[J]. IEEE Trans. on Industry Applications, 1981, 17(5): 518-523.

- [4] Mondal S K, Bose B K, Oleschuk V, et al. Space vector pulse width modulation of three-level inverter extending operation into overmodulation region[J]. IEEE Transactions on Power Electronics, 2003, 18(2): 604-611.

- [5] 金舜,钟彦儒.一种新颖的同时考虑中点电位平衡和窄脉冲消除及 死区补偿的三电平空间电压矢量脉宽调制方法[J]. 中国电机工程学 报, 2005, 25(6): 60-66.

- Jin Shun, Zhong Yanru. A novel three-level SVPWM algorithm considering neutral-point control and narrow-pulse elimination and dead-time compensation[J]. Proceedings of the CSEE, 2005, 25(6): 60-66(in Chinese).

- [6] 毛承雄,李维波,陆继明,等. 高压变频器共模电压仿真研究[J]. 中 国电机工程学报, 2003, 23(9): 57-62. Mao Chengxiong, Li Weibo, Lu Jiming, et al. Study of the

- common-mode voltage in a high-voltage ASD's system [J]. Proceedings of the CSEE, 2003, 23(9): 57-62(in Chinese).

- [7] Li Haishan, Li Yaohua, Ge Qiongxuan. Dead-time compensation of 3-level NPC inverter for medium voltage IGCT drive system[C]. IEEE Power Electronics Specialists Conference, Achen, Germany, 2004.

- [8] Liu Jian, Yin Xianggen, Zhang Zhe, et al. Study on protection measures of SPWM for power electronic devices of high voltage three-Level NPC inverter[C]. APAP 2007, Jeju Korea, 2007.

- [9] Liu Jian, Zhang Zhe, Yin Xianggen, et al. Fpga implementation of a multi-level SPWM for three-level NPC inverter[C]. UPEC 2006, Newcastle, UK, 2006.

- [10] Tzou Y Y, Hsu H J. FPGA realization of space-vector control IC for three-Phase PWM inverters[J]. IEEE Trans. on Power Electronics, 1997, 12(6): 953-963.

- [11] Tonelli M, Battaiotto P, Valla M I. FPGA implementation of an universal space vector modulator[C]. IECON'01, Denver, USA, 2001.

- [12] 宋强,刘文华. 基于零序电压注入的三电平 NPC 逆变器中点电位 平衡控制方法[J]. 中国电机工程学报, 2004, 24(5): 58-62. Song Qiang, Liu Wenhua. A neutral-point potential balancing algorithm for three-level NPC inverters by using analytically injected zerosequence voltage[J]. Proceedings of the CSEE, 2004, 24(5): 58-62(in

- [13] 费万民,吕征宇,姚文熙. 三电平逆变器特定谐波消除脉宽调制方 法的研究[J]. 中国电机工程学报, 2003, 23(9): 11-15. Fei Wanmin, Lü Zhengyu, Yao Wenxi. Research on selected harmonic elimination PWM technique applicable to three-level voltage inverters[J]. Proceedings of the CSEE, 2003, 23(9): 11-15(in Chinese).

- [14] 林磊, 邹云屏, 钟和清, 等. 二极管箝位型三电平逆变器控制系统 研究[J]. 中国电机工程学报, 2005, 25(15): 33-39. Lin Lei, Zou Yunping, Zhong Heqing, et al. Study of control system of diode-clamped three-level inverter[J]. Proceedings of the CSEE, 2005, 25(15): 33-39(in Chinese).

- [15] 毛惠丰,陈增禄,任记达,等. SPWM 数字化自然采用法的理论及 脉冲误差分析[J]. 中国电机工程学报, 2006, 26(9): 131-136. Mao Huifeng, Chen Zenglu, Ren Jida, et al. Theory and pulse error study of digital natural sampling based SPWM[J]. Proceedings of the CSEE, 2006, 26(9): 131-136(in Chinese).

Chinese).

作者简介:

收稿日期: 2007-10-24。

刘健(1979一), 男, 博士研究生, 研究方向为 大功率电力电子变换系统及其应用、电力系统继电 保护等, 163ted@163.com;

尹项根(1954一), 男, 教授, 博士生导师, 主要 研究领域为电力系统继电保护与安全稳定控制,信 息、光电、电力电子技术及其在电力工程中的应用; 张哲(1962--), 男, 教授, 博士生导师, 主要 研究领域为电力系统继电保护与安全稳定控制、 FACTS 技术、电机控制等;

熊卿(1980一), 男,博士研究生,主要研究方 向为大功率电力电子变换系统及其控制技术。

王彦骏)