工程应用技术与实现。

文章编号: 1000-3428(2012)04-0205-03

文献标识码: A

中图分类号: TP302.8

# 基于扫描链阻塞技术的时延测试方法

#### 王泽成, 尤志强

(湖南大学软件学院,长沙 410082)

**摘 要:** 针对时延测试功耗和测试费用较高的问题,提出一种低费用的轮流捕获时延测试方法。采用扫描阻塞技术,将被测电路中的所有扫描单元分成多条子扫描链,使电路中每时刻只有一条子扫描链活跃。在进行故障测试时,通过阻塞一部分子扫描链,使扫描单元得到充分利用。实验结果表明,该方法能降低测试应用时间和测试数据量,且硬件开销较少。

关键词: 时延测试; 可测性设计; 低费用测试; 扫描链阻塞技术

## Delay Test Method Based on Scan Chain Blocking Technique

WANG Ze-cheng, YOU Zhi-qiang

(Software School, Hunan University, Changsha 410082, China)

[Abstract] In order to solve the high test cost and high test power, the study proposes a low cost test method. Using scan chain blocking technique, all sequence elements are divided into N scan sub-chains and only one scan sub-chain is active at a time during scan test. Not all elements need to be active in test. The division of sub-chain makes some sequence elements inactive in test model and make full use of scan elements. Experimental result demonstrates that the method can drastically reduce test application time with a low cost on hardware.

[Key words] delay test; Design for Test(DFT); low cost test; scan chain blocking technique

DOI: 10.3969/j.issn.1000-3428.2012.04.067

#### 1 概述

随着超大规模集成技术的迅猛发展,集成电路的规模成指数倍增加,工作频率的不断增加,给集成电路的测试带来了更多挑战:一方面是测试功耗过高和测试成本增加;另一方面是时延故障对电路的影响越来越大,使时延测试成为热门课题之一。

全扫描设计是为了降低测试生成复杂性的最重要可测性设计方法之一,其主要思想是获得对触发器的控制和可观察性。这是通过对电路增加一个测试模式,使电路工作于测试模式时,电路中所有触发器在功能上构成一条或多条扫描链。通过移位寄存器的移位方法或其他方法将触发器置位,可以把所有的触发器设定为任意状态。同样,也可以通过将触发器的内容移位观察触发器的逻辑值。因此,基于全扫描的数字电路测试应用时间与电路中的扫描链长度呈正比,虽然可以降低测试生成的复杂性,但是测试应用时间太长,测试功耗过高,甚至比正常工作模式下的功率消耗还要大[1-3],影响电路的可靠性。因此,降低测试应用时间和测试功耗是数字电路测试中丞需解决的问题之一。

最近一些低费用测试技术陆续出现<sup>[4-8]</sup>,文献[4]利用电路中扫描单元间的相容关系降低测试应用时间,通过考虑部分扫描链的相容性,适当调整测试向量的顺序改进其测试方案,显著降低测试应用时间。文献[5]利用轮流捕获方案降低测试应用时间。文献[6-7]更改阻塞结构达到降低测试费用的目的。文献[8]基于阻塞技术对扫描子链进行跳变时延故障实验,认为对扫描链分组不仅可以降低测试功耗,而且可以提高故障覆盖率。然而这些方法中有些是基于固定故障,有些需要额外控制信号,从而增加测试数据量,使测试费用增加。本文在这些方法上探讨时延低功耗低费用技术,采用扫描阻塞技术降低测试功耗,采用增加两测试向量之间的关联度降

低测试应用时间,使用轮流捕获方案,再适当地修改测试流程,实现了一种新的测试应用时间的方法。

### 2 阻塞技术

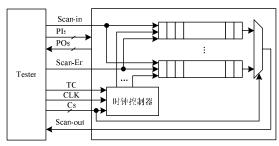

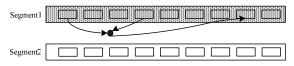

阻塞技术测试方案如图 1 所示。

图1 阻塞技术测试方案

扫描单元被分成 N 条扫描链,添加输入端口 TC 和 Cs、时钟控制器和 MUX。在测试模式下(TC=1),时钟控制器将系统时钟 CLK 仅分配给一条扫描链。当 Scan\_En 同时为 1 时,该扫描链扫描移入测试向量同时移出测试响应。因此,这种模式可以同时降低扫描测试中的平均功耗和峰值功耗。在正常工作模式下(TC=0),CLK 被传递给所有的扫描链而实现正常操作。

在该方案中,通过配置 Cs,使 CLK 经过时钟控制器轮流激活扫描子链,将一个测试向量逐个扫入每一条子链。然后通过配置 Cs,使 CLK 经过时钟控制器,激活一条指定的扫描子链捕获测试响应。

基金项目: 国家自然科学基金资助项目(60673085)

作者简介:王泽成(1986-),男,硕士研究生,主研方向: SoC 测试

与设计; 尤志强, 副教授、博士

**收稿日期:** 2011-05-20 **E-mail:** wangzecheng@126.com

#### 3 扫描链阻塞技术在时延测试中的应用及改进

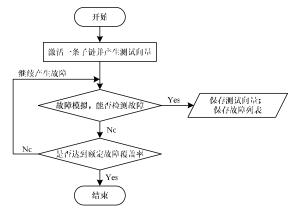

由于传统的测试生成算法不能对这种结构生成测试向量,因此本文修改了 TetraMAX 的测试流程,对标准电路 s5378 进行实验,测试向量产生流程见图 2。

图 2 测试向量产生流程

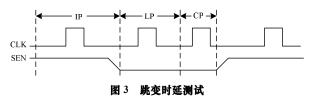

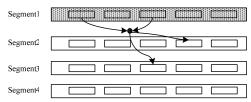

跳变时延故障的测试(如图 3 所示)向量需要一对向量(V1, V2),整个测试过程分成 3 个部分:

- (1)initialisation phase(IP), 在这个时间段, V1 被输入。

- (2)launch phase(LP), V2 是从这个时间段获得或者输入。

- (3)capture phase(CP), 获得输出。

扫描单元被分成 N 条扫描链, 首先激活第 1 条扫描链, 使用 TetraMax 对其产生测试向量, 保存相关的测试向量和故障列表, 然后第 2 条扫描链被激活, 其他的扫描链保持不变, 产生相应的测试向量……到第 N 条扫描链都活跃时, 接下来第 1 条扫描链将被激活。

图 3 显示的是跳变时延测试,CLK 和 SEN 分别为时钟信号和使能信号,在 IP 时钟,V1 被扫入扫描链;在 LP 时钟,V2 由捕获产生;CP 时钟产生测试输出。

在传统时延测试过程中,所有扫描单元都被激活,而使 用阻塞技术的时延测试分成多条子链,时延测试轮流捕获规 则有:

- (1)任何时刻只有一条扫描子链是活跃的。

- (2)扫描子链轮流活跃。

- (3)输出捕获和初始测试向量扫入是同一条子链。

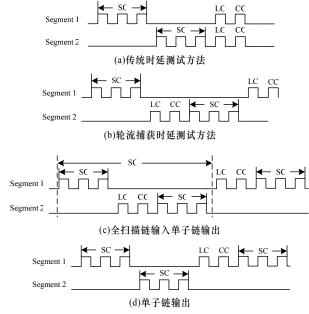

图 4(a)表示在 LOC(Latch on Capture)传统时延测试方法下的时序,当所有的扫描链都被扫入数据后,才会被捕获产生 V2,因此,它的可控性和可观察性达到最大,故障覆盖率最好。

在图 4(b)中,当有一条扫描链被扫入数据时,就会产生捕获,获得输出,但是其可控性和可观察性也相应降低,在对 s5378 的初步实验中,虽然测试平均功耗和测试时间分别降低 82.3%和 87.1%,但是其跳变时延故障覆盖率只有64.9%,因此,需要修改测试产生算法来适应这种结构。由于修改完整算法的复杂性,因此改进了测试过程,在不降低故障覆盖率的情况下降低测试应用时间,如图 4(c)所示。

在图 4(c)中,考虑从第 1 条到最后一条链激活过程,由

于初始向量扫入扫描链的时间(SC)远大于捕获(LP、CP)的时间,而捕获的是下一条扫描链,因此并没有改变当前触发器的值,从N个时钟周期来看,这是对整个扫描链做输入,即所有的扫描单元是可控的,这样就大幅度增加扫描单元的可控性,实验结果表明,总测试功耗和测试时间有明显下降。

如果考虑到扫描移位输入时间远大于捕获时间,把从第1条扫描链到最后一条扫描链依次活跃的情况看做一个整体,那么相当于先对整个扫描链做扫描输入,如图 4(d)所示。

图 4 不同时延测试方法的时序图

#### 4 实验结果与分析

本文利用 Synopsis 的 TetraMax 编写 perl 和 tcl 脚本对 ISCAS89 的 s5378 做实验,采用跳变故障模型,测试向量使用随机填充,得到的结果见表 1。

表 1 传统测试方法和轮流捕获测试方法的性能比较

| 测试方法    | 峰值跳变数 | 总跳变数      | 测试应用时间/时钟周期 |

|---------|-------|-----------|-------------|

| 传统方法    | 123   | 4 472 822 | 44 268      |

| 子链数 N=3 | 70    | 805 552   | 19 085      |

| 子链数 N=4 | 56    | 668 818   | 19 096      |

| 子链数 N=5 | 42    | 689 563   | 36 175      |

| 子链数 N=6 | 38    | 358 653   | 20 765      |

由表 1 可以看出,峰值跳变数与子链数有关,由于扫描单元个数是一定的,分的越多,每条子链的扫描单元就越少,峰值跳变数就越少,测试时间并没有随子链数增加而急剧减少,这表明跳变故障的激活需要一定的 D 触发器(D Flip Flop, DFF)确定值,即可观察度(DFF 数)并没有减少,这表明测试时间的减少来自于相邻两测试向量中相同部分,而这个相同部分是一定的。

因此不可能无限制地降低测试应用时间,同样通过修改测试生成算法也只能降低到一定程度,而且当子链数增大时,捕获的时间(LP、CP)在测试应用时间的比重也在增加,直接影响到测试应用时间的改善。

在不同规模电路中,阻塞技术对于时延测试应用时间的 影响见表 2,其中,扫描子链数为 3 条,如果测试向量中存 在无关位,使用随机填充,可以看出当电路规模增大时故障 覆盖率也会提高,电路规模越大,越能从阻塞技术中获得更 好的效果,测试应用时间也下降得越多。

| 表 2 | 不同的 | 1路规模 | 的测试 | 应用时间 |

|-----|-----|------|-----|------|

|     |     |      |     |      |

|   | 电路     | 子链数 | 故障覆盖率/(%) | 测试应用时间降低比率/(%) |

|---|--------|-----|-----------|----------------|

| - | s298   | N=3 | 56.6      | 68.5           |

|   | s1423  | N=3 | 98.3      | 53.3           |

|   | s5378  | N=3 | 77.9      | 72.1           |

|   | s9234  | N=3 | 87.9      | 80.0           |

|   | s13207 | N=3 | 82.3      | 81.9           |

从表 2 可看出,对于 s1423 而言,其故障覆盖率达到 98.3%,比其他高得多,这说明 N=3 对 s1423 是适合的,下面分析 s13207 电路在不同子链数的分析情况,见表 3。

表 3 不同子链数的测试应用时间

| 电路     | 子链数 | 故障覆盖率/(%) | 测试应用时间降低比率/(%) |

|--------|-----|-----------|----------------|

| s13207 | N=2 | 72.3      | 84.1           |

| s13207 | N=3 | 82.3      | 81.9           |

| s13207 | N=4 | 88.4      | 84.0           |

| s13207 | N=5 | 89.6      | 86.3           |

| s13207 | N=6 | 91.3      | 87.3           |

| s13207 | N=7 | 90.6      | 87.8           |

| s13207 | N=8 | 89.5      | 88.8           |

可以看出,当扫描子链数增大到适当的数量时,其故障覆盖率达到最大,对于 s13207 而言,当子链数 N=6 时,其覆盖率达到最大。之后,随着子链数的增加反而下降,其原因为:影响测试故障覆盖率响应的主要因素是该故障的激励触发器和捕获响应触发器。

(1)在当子链数较低时,这使得子链较长,由于采用在下一个子链捕获测试响应,一旦故障测试响应是传递到本链捕获输出,那么该故障是不可测,如图 5 所示。

图 5 故障响应传递到当前链的情况

(2)在子链数较多时,每条子链的扫描单元较少,可能激活故障或捕获测试响应需要多条链,如图 6 所示。

图 6 故障响应需要多条链同时捕获的情况

#### 5 结束语

本文研究了阻塞技术对时延测试中测试应用时间的影响。针对 ISCA89 标准电路中一些电路做了不同电路规模的故障覆盖率和测试应用时间的比较,当电路规模较大时,使用阻塞技术可以大幅度地降低测试应用时间,而故障覆盖率也越来越大。对于同一电路 s13207,在子链数适当时其故障覆盖率最大,而测试应用时间下降达 80%且平稳。

这些实验结果都表明结合轮流捕获方案的阻塞技术能有 效降低时延测试应用时间,尤其适合大电路。今后将在基于 轮流捕获方案的阻塞技术下,分析扫描单元规模和分链数在 何种情况下的故障覆盖率达到最大。

#### 参考文献

- [1] Zorian Y. A Distributed BIST Control Scheme for Complex VLSI Devices[C]//Proc. of the 11th VLSI Test Symposium. Atlantic City, USA: [s. n.], 1993: 4-9.

- [2] Girad P. Survey of Low-power Testing of VLSI Circuits[J]. IEEE Design Test of Computers, 2002, 19(3): 82-92.

- [3] Roy K, Prasad S. Low-power CMOS VLSI Circuit Design[M].

[S. l.]: John Wiley & Sons, 2000.

- [4] Dai Gui, You Zhiqiang, Kuang Jishun, et al. DCScan: A Power-aware Scan Testing Architecture[C]//Proc. of the 17th Asian Test Symposium. Sapporo, Japan: [s. n.], 2008: 343-348.

- [5] You Zhiqiang, Huang Jiedi, Inoue M, et al. Capture in Turn Scan for Reduction of Test Data Volume, Test Application Time and Test Power[C]//Proc. of the 19th IEEE Asian Test Symposium. Washington D. C., USA: IEEE Press, 2010: 371-374.

- [6] 张 云, 尤志强, 邝继顺, 等. 基于TSP的低功耗低费用测试方法[J]. 计算机工程, 2011, 37(4): 281-283.

- [7] 江招生, 尤志强, 张大方, 等. 一种基于TSP问题的扫描链阻塞 技术低费用测试方法[J]. 哈尔滨工业大学学报, 2009, 41(1): 176-179.

- [8] Zhang Z, Reddy S M, Pomeranz I, et al. Enhancing Delay Fault Coverage Through Low Power Segmented Scan[J]. Computers & Digital Techniques, 2006, 3(1): 21-28.

编辑 陆燕菲

#### (上接第 201 页)

#### 参考文献

- [1] Buades A, Coll B, Morel J M. A Review of Image Denoising Algorithms with a New One[J]. Multiscale Modeling & Simulation, 2005, 4(2): 490-530.

- [2] Buades A, Coll B, Morel J M. Image Denoising Methods. A New Nonlocal Principle[J]. SIAM Review, 2010, 52(1): 113-147.

- [3] 闵 涛, 黄 娟. 图像去噪中的有限元求解方法[J]. 计算机工程, 2011, 37(9): 234-235.

- [4] Lai Rui, Dou Xuan-xuan. Improved Non-local Means Filtering Algorithm for Image Denoising[C]//Proc. of CISP'10. Yantai,

- China: [s. n.], 2010.

- [5] Park S W. NLM Algorithm with Weight Update[J]. Electronics Letters, 2010, 46(15): 1061-1062.

- [6] Tian Jing, Yu Weiyu, Xie Shengli. On the Kernel Function Selection of Nonlocal Filtering for Image Denoising[C]//Proc. of IEEE Int'l Conf. on Machine Learning and Cybernetics. Kunming, China: [s. n.], 2008.

- [7] Buades A, Coll B, Morel J M. Nonlocal Image and Movie Denoising[J]. International Journal of Computer Vision, 2008, 76(2): 123-139.

编辑 陈 文