# Spatially Modulated Photodetector in an Unmodified 0.13 µm CMOS-Process

M. Jutzi, E. Gaugler, M. Berroth

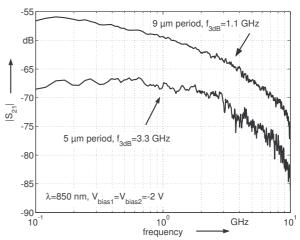

*Abstract*—Photodetectors fabricated in an unmodified, commercially available CMOS-process are reported. The detector comprises an immediate and a shaded n-well to p-substrate photodiode. S-parameter measurements indicate a 3dB-bandwidth of 1.1 GHz at a photoresponsivity of 20 mA/W to 850 nm light. Two different geometrical layouts are investigated experimentally.

*Index Terms*—CMOS-photodiode, CMOS-OEICs, optical receiver

#### I. INTRODUCTION

In the last decades Silicon-CMOS has turned out to be the technology of choice to realize complex digital and analog integrated circuits. Monolithic integration of formerly hybrid circuits has led to reduced geometrical dimensions, low weight and high reliability at low cost.

Optical interconnects offer superior bandwidth and are virtually immune to electromagnetic interference. They are already widely used to build local-area-networks (LANs). In the near future they might be used to distribute time-critical signals, i.e. the clock of a processor, to several units on a backplane or to logic gates on a chip.

Low-cost vertical cavity surface emitting lasers (VCSELs) are easily available as directly modulated light sources at a wavelength of 850 nm. However, radiation of this wavelength has a 1/e-penetration depth of about 16  $\mu$ m in Silicon and thus generates only few charge carriers in the regions close to the surface, where pn-junctions are defined by the CMOS-process. This problem becomes even more severe in the future, because the junction depth decreases as the minimum feature sizes are reduced from one CMOS-generation to the next.

Several groups have used modified CMOS-processes to design fast photodetectors with high photoresponsivities. This paper however focuses on detectors in standard, unmodified CMOS-processes in order to benefit from the inherent cost advantage [1]-[6]. For many applications low fabrication cost might be more important than optimum device performance.

#### II. PHOTODETECTOR LAYOUT AND CROSS-SECTION

The spatially modulated CMOS-detector has been implemented in a  $0.13 \,\mu m$  CMOS technology. This novel type of detector has been proposed and realized in the

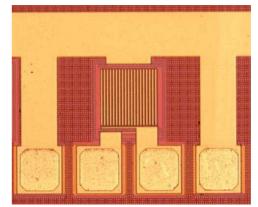

literature [7]. The photodetector features a ground-signal-signal-ground contact pattern as shown in the chip micrograph of Fig. 1. The dimensions of the active area are  $100 \,\mu m \times 100 \,\mu m$  for optical coupling with relaxed alignment tolerances.

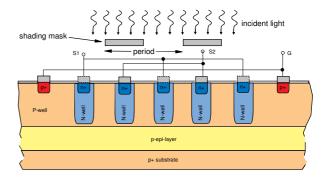

The detector comprises two photodiodes: One diode is directly illuminated and the other is shaded by a floating metal mask as presented in the cross section of Fig. 2. The photodiode comprises the junction between the n-well and the lightly doped p-substrate. The high contrast of the doping concentrations between n-well and substrate makes sure that the space charge region mainly extends into the substrate. Drift and diffusion currents contribute to the photoresponse of the illuminated detector, whereas diffusion currents dominate the response of the shaded detector. In the differential signal the slow diffusion components of the photoresponse are cancelled out. Thus, the differential signal is much faster than the individual single ended signals. Photodetectors with a period of the shading mask of 5  $\mu$ m and 9  $\mu$ m have been fabricated.

Fig. 1. Layout of the spatially modulated photodetector.

Fig. 2. Schematic device cross section of the spatially modulated photodetector.

## **III. IV-CHARACTERISTICS**

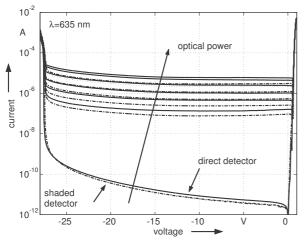

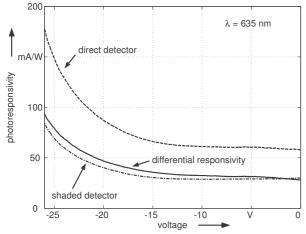

The current-voltage characteristics are measured with a semiconductor parameter analyzer HP4155B for different incident optical powers at wavelengths of 635 nm and 850 nm. Both the immediate and the deferred diode exhibit nearly equal dark currents and a low dark current density normalized to the active area of  $1.96 \,\mu$ A/cm<sup>2</sup>. Breakdown occurs above a reverse bias voltage of 27.5 V as can be seen in Fig. 3. For the 9  $\mu$ m period device the differential steady-state photoresponsivity attains 20 mA/W at 850 nm and 34 mA/W at 635 nm at 2 V reverse bias. Avalanche gain begins to enhance the photoresponse at -15 V as illustrated in Fig. 4.

Fig. 3. IV-characteristics of the device with a  $9 \,\mu m$  period for different optical powers at 635 nm.

Fig. 4. Photoresponsivity to unmodulated light of 635 nm, device with a  $9 \mu m$  period.

Table I gives an overview of the DC-responsivities at the relevant wavelengths of 635 nm and 850 nm.

Table I: Processed Samples

| Period | Responsivity at | Responsivity at | 3dB- bandwidth at |

|--------|-----------------|-----------------|-------------------|

| [µm]   | -2 V, 635 nm    | -2 V, 850 nm    | -2 V, 850 nm      |

|        | [mA/W]          | [mA/W]          | [GHz]             |

|        | immediate/      | immediate/      |                   |

|        | deferred/       | deferred/       |                   |

|        | differential    | differential    |                   |

| 5      | 49/ 39/ 10      | 33/ 28/ 5       | 3.3               |

| 9      | 69/ 35/ 34      | 47/ 27/ 20      | 1.1               |

### IV. TRANSFER FUNCTION AND IMPULSE RESPONSE

The opto-electrical transfer function has been measured with an HP8510C network analyzer. Port one drives a 10 Gbit/s vertical cavity surface emitting laser at 850 nm and port two is connected to the photodetector under test. For on-wafer characterization GSSG Cascade-Microtech probe tips are used.

The photoresponse is dominated by the current of the minority carriers, i.e. the electrons in the p-substrate. The bandwidth of the opto-electrical transfer function of a conventional n-well to p-substrate detector is limited by diffusion. By introducing a periodic illumination pattern the low-frequency response of the differential signal is damped [8].

Fig. 5. Transfer function of the photodiodes with a period of 5  $\mu$ m and 9  $\mu$ m at 850 nm for a reverse bias voltage of 2 V.

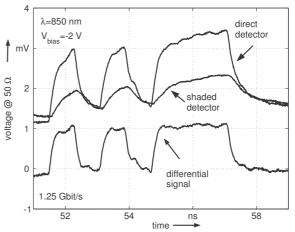

Fig. 6. Photoresponse to a 1010111 bit sequence at a clock rate of 1.25 Gbit/s, a reverse bias voltage of 2 V and an incident wavelength of 850 nm.

By reducing the period of the shading mask from  $9 \mu m$  to  $5 \mu m$  the 3dB-bandwidth increases from 1.1 GHz to 3.3 GHz as can be seen in Fig. 5. The photodector with the larger period is more appropriate for an application because the responsivity is 4 times higher.

The bandwidth increases near the breakdown voltage. The 9  $\mu$ m period device exhibits a 3dB-bandwidth of 2.5 GHz at a reverse bias voltage of 26 V. The avalanche gain is more than 2.

Impulse response measurements are performed at a

wavelength of 850 nm using an Anritsu MP1763C bit pattern generator and an HP54750A digitizing oscilloscope. In the differential signal in Fig. 6 no slow diffusion tails are observed thus demonstrating the effectiveness of the cancellation mechanism. The measurements indicate that data transmission at 1.25 Gbit/s and a wavelength of 850 nm should be possible even for a small reverse bias voltage of 2 V.

# V. CONCLUSION

A spatially modulated photodetector has been implemented in a commercially available, unmodified  $0.13 \,\mu\text{m}$  CMOS-process. The differential photodiode concept works as a built-in equalizer. This type of photodetector is very appropriate for monolithic integration with an amplifier, because only a small reverse bias voltage is needed, which could be easily provided on-chip. The detector speed is expected to increase if red VCSEL sources are used, which might be widely available soon.

#### REFERENCES

- T. K. Woodward, A. V. Krishnamoorthy: 1-Gb/s Integrated optical detectors and receivers in commercial CMOS technologies, IEEE J. of Selected Topics in Quantum Electronics, Vol. 5, No. 2, March/April 1999, pp. 146-156

- [2] P.J.-W. Lim, A.Y.C. Tzeng, H. L. Chuang, S.A. St. Onge: A 3.3-V monolithic photodetector/CMOS-preamplifier for 531 Mb/s optical data link applications, Solid-State Circuits Conference, 1993. Digest of Technical Papers. 40th ISSCC., 1993 IEEE International, 1993, pp. 96 -97, 268

- [3] L.D. Garrett, J. Qi, C. L. Schow, J. C. Campbell: A silicon-based integrated NMOS-p-i-n photoreceiver, IEEE Transactions on Electron Devices, Vol. 43, No. 3, March 1996, pp. 411-416

- [4] C. L. Schow, J. D. Schaub, R. Li, J. Qi, J. C. Campbell: A monolithically integrated 1-Gb/s silicon photoreceiver, IEEE Photonics Technology Letters, Vol. 11, No. 1, Jan. 1999, pp. 120-121

- [5] H. Zimmermann, T. Heide, A. Ghazi: Monolithic high-speed CMOS photoreceiver, IEEE Photonics Technology Letters, Vol. 11, No. 2, February 1999, pp. 254-255

- [6] C. Hermans, P. Leroux, M. Steyaert: Gigabit photodiodes in standard digital nanometer CMOS technologies, 33rd European Solid-State Circuits Conference, ESSDERC 2003

- [7] M. Kuijk, D. Coppee, R. Vounckx: Spatially modulated light detector in CMOS with sense-amplifier receiver operating at 180 Mb/s for optical data link applications and parallel optical interconnects between chips, IEEE J. Select. Topics Quantum Electron., Vol. 4, Dec 1998, pp. 1040-1045

- [8] J. Genoe, D. Coppée, J. H. Stiens, R. A. Vounckx, M. Kuijk: Calculation of the current response of the spatially modulated light CMOS detector, IEEE Transactions on Electron Devices, Vol. 48, No. 9, September 2001, pp. 1892-1902