• 多媒体技术及应用 •

Vol.34 No.7 Computer Engineering

中**图**分类号: TH166

# 低速率可重构声码器的研究与设计

文章编号: 1000-3428(2008)07-0235-03

荆 涛,王 沁,赵宏智

(北京科技大学信息工程学院,北京 100083)

摘 要:为满足数字语音通信对高性能和高灵活性的应用需求,设计一种基于 SELP 语音编解码算法的具有可重构、高并行度、可编程、安全性等特点的声码器。介绍了该声码器的功能、设计目标、特征设计及其体系结构设计,并对四级可重构的 ALU 单元、数据通路单元等功能部件以及可变长 VLIW 专用指令集的设计进行描述。

关键词: 声码器; 可重构; 超长指令字

# Research and Design of Low Rate Reconfigurable Vocoder

JING Tao, WANG Qin, ZHAO Hong-zhi

(Information Engineering School, University of Science and Technology Beijing, Beijing 100083)

[Abstract] For the purpose of high performance and high flexibility of digital speech communication, this paper expatiates one kind of special purpose processor for speech compression based on SELP algorithm, which characterizes reconfigurable, high degree of parallelism, programmable and safety. It discusses the main function, design goal, character design and architecture of the vocoder, and expands on the design of a variable length VLIW instruction set and function units, such as four-stage reconfigurable ALUs and data-path units.

【Key words 】 vocoder; reconfigurable; VLIW

# 1 概述

当前使用的电话绝大多数仍属于模拟电话,随着数字通信业的迅速发展,人们希望能够在 Internet 和综合业务数字网上传送语音信号;另一方面,在信息的存储、传输与处理的过程中,有关如何保护信息使之不被非法窃取或篡改,得到人们的关注。因此,提出了数字保密电话的要求。

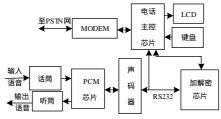

通常,数字保密电话终端设备主要包括声码器、加解密芯片、调制解调器等组成模块。在本项目设计的数字保密通信终端系统中,声码器是一个非常重要的组成部分,如图 1 所示。在实际通信中,为适应多种应用环境,声码器需要使用不同的语音编解码算法。如果使用ASIC完成算法实现,则只能实现单一算法,无法扩展于其他算法,不利于算法的升级与维护<sup>[1]</sup>;如果利用DSP编程实现,则存在编程难、成本高、保密性差等缺点<sup>[2]</sup>。因此,本文设计了一种低速率可编程、具有可重构数据路径的声码器。

图 1 数字保密通信终端中的声码器

### 2 声码器的功能

该声码器的功能就是实现一种基于SELP(Sinusoidal Excitation Linear Prediction)的多帧联合编码算法<sup>[3]</sup>,对数字语音信号进行编码和解码处理。该算法由清华大学开发,是在线性预测正弦激励模型的基础上,引入多帧参数联合矢量量化方法,进一步压缩帧间冗余,使语音谱包络信息和余量

信号得到较好表示,在 0.6 Kb/s的极低速率下能获得很好的重建语音质量,可懂度达到 90%以上。根据不同的信道状况与质量要求,该算法还包括 0.8 Kb/s, 1.2 Kb/s和 2.4 Kb/s 3种速率的编码方式,流程与 0.6 Kb/s算法基本相同。

文献标识码: A

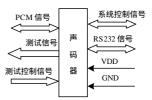

为实现该算法功能,声码器的外部接口如图 2 所示。与PCM 采样芯片的接口包括数据接口(含数据缓冲区)与控制接口,可以与指定型号的 PCM 芯片直接连接,也可以在外接专用控制芯片的前提下使用同步接口连接其他类型的 PCM 芯片。编码、解码流经由 RS232 接口(含数据缓冲区)与加解密芯片相连接。此外,声码器外部接口还包含测试接口、注入接口、异步复位接口、系统控制接口等。

图 2 声码器外部接口

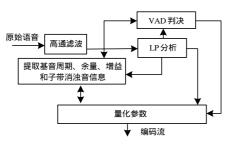

声码器的编解码功能如图 3 所示,描述如下:

(1)编码功能

1)声码器接收来自 PCM 采样芯片数据缓冲器中的原始语音,采样频率为 8 kHz,对每个采样点进行 16 bit 量化。

2)声码器对 PCM 送来的语音数据进行编码处理 ,形成编码数据流。根据芯片上电时配置文件的不同 , 编码流可分为

基金项目: 国家自然科学基金资助项目(60572081)

**作者简介:**荆 涛(1978-),男,博士研究生,主研方向:计算机体系结构,集成电路设计;王 沁,教授、博士生导师;赵宏智,博士研究生

**收稿日期:**2007-04-13 **E-mail:**jingtao.1978@163.com

- 0.6 Kb/s, 0.8 Kb/s, 1.2 Kb/s 和 2.4 Kb/s 4 种规格。

- 3)编码数据流送入 RS232 缓存。

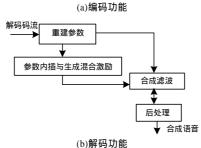

- (2)解码功能

- 1)声码器接收来自 RS232 端口的数据流,数据流的速率可为 0.6 Kb/s, 0.8 Kb/s, 1.2 Kb/s 和 2.4 Kb/s 4 种规格。

- 2)声码器对输入数据进行解码处理,形成解码数据流。

- 3)解码数据流送入 PCM 缓存。

图 3 SELP 算法编、解码功能

# 3 声码器的设计目标

为实现上述算法功能,该声码器总体设计目标是:满足党、政、军机关办公自动化的安全通信要求以及商业、金融等领域的信息传输安全要求,满足网络电话、卫星通信、移动通信等对带宽要求较高的应用需求,并满足低成本、易开发等设计需求。

该声码器的应用特征需求描述如下:

- (1)可重构:可重构的声码器能够利用可重用的硬件资源,根据不同的应用需求,灵活地改变自身体系结构,以较少的规模实现多种语音编解码算法,在满足性能要求的前提下提高芯片的灵活性,使之具有良好的应用前景。

- (2)高并行度:为满足语音通信的实时性,声码器芯片应具备较高的并行度,在一个时钟周期内完成多种可并行操作。

- (3)可编程:各领域的计算机应用都在不断更新变化,语音通信领域对算法的要求也在不断提高,因此,声码器芯片应能够根据需求的变化对算法进行改进或者替换,具备可编程的特性。

- (4)安全性:声码器内部的语音算法程序实现应保证不能被读取,同时配合加解密芯片,有效保障语音传输的安全性。

#### 4 声码器的特征设计

上述应用特征需求的特征设计描述如下:

(1)可重构:为了适应不同语音算法的硬件实现的需要,同时能高效灵活地实现运算、存储等部件之间的数据交换,需要设计一种可重构数据路径,实现存储器、运算部件、寄存器堆等部件之间输入输出路径的可重构。这些可重构路径由译码器通过执行指令进行控制。该数据路径结构中的指令字长、处理单元个数和互联网都是可变的,是结构级可重构的,所以它具有粗粒度和结构级可重构处理系统的优点,适

合语音算法这类有规律、高重复性和计算密集型的任务。

- (2)高并行度:在分析各类语音算法后,发现语音算法的运算具有天然的高并行性,因此适合采用硬件予以并行实现,同时,在低主频设计下达到算法的高效实现,提高并行度也是很有必要的,应从如下几个方面进行考虑:

- 1)足够带宽的数据通路部件。

- 2)能并行发出控制信号的控制部件,如超长指令译码器。

- 3)多个功能相同或相似的运算或存储部件。

- (3)可编程:可编程的声码器能方便地通过改变算法指令程序来实现算法的升级,应具备可扩充的指令集,对算法中运算量大、重复性高的程序部分,可用新的专用指令来实现,或者在原有专用指令的基础上,通过改变原有指令的语义来实现,其他部分可以用基本指令集进行实现。

- (4)安全性:语音算法存储在片内 FLASH 中,只能通过注入方式进行修改而不能读取,可有效保障算法的安全性;使用 FLASH 作为固定码本的存储器,利用其具备可擦写的特性来获得数据级别的可重装载功能;不设置外部可见数据总线,以防止算法程序与数据泄漏。

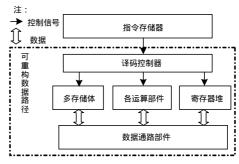

# 5 声码器体系结构

结合 SELP 算法及其他常用语音算法的运算特点,提取各类算法共有的运算功能,以及分析声码器的应用特征之后,本着适应多种语音编解码算法的实现、程序便于升级、适应国产化水平的原则,设计了一种具有可重构数据路径的声码器体系结构,如图 4 所示。

图 4 声码器体系结构

该声码器的设计工作主频为 20 MHz,采用取指-译码-执行的 3 级流水线设计,其中取指模块为适应可变长的 VLIW指令而采用 4 倍频技术。该体系结构主要由以下部分组成:

- (1)存储系统:采用多存储体设计,以满足语音算法中大量矢量计算的并行运算需要。定点语音算法对 16 位数组的运算需求一般是两读一写,在硬件体系上支持 3 个数组同时读写的操作,则可提高矢量运算的效率与运算并行度;为提高计算精度,有时会使用 32 位数组来进行矢量运算,但这时多为一读一写。综合这 2 种数据操作的需求,设计了如下多存储体结构:5 块单端口 2 K×16 bit 的 SRAM,用于存放中间计算结果和临时数据,同时,前 2 块存储器可以两两合并为 2 个 32 位存储器进行读写;2 块 16 K×16 bit 的 FLASH,用于存放码本数据。各存储器的输入数据源为:每个存储器的输出,来自数据通路部件的数据;其输出数据流向为:各存储器的输入,通过数据通路部件连到各运算部件和寄存器堆。

- (2)运算部件:由于语音编解码算法是运算密集型应用, 因此设计了2个ALU单元、1个乘法单元、1个乘累加单元, 1个除法/位运算混合单元和1个比较置位单元等6个功能单元,各功能单元都有独立的结果锁存器。定点语音编解码算

法以 16 位数据为基本处理带宽,因此运算部件应同时具备对 16 位、32 位数据进行操作的能力。所有运算单元的输入数据源是各数据通路部件的输出,输出数据流向是各数据通路部件的输入,不直接与存储器或寄存器堆相连。

ALU 单元应具备功能:加,减,四舍五入,绝对值,取 反,移位,比特计算等。在语音算法中经常出现3个操作数 相加减或加减运算后执行规格化移位等复合操作,运算复杂 度较大,表1中列出了一些常见的复合运算操作。同时,在 声码器的 3 级流水线中, ALU 与乘法器同属于执行级, 而同 一流水级内的部件延时如果相近,则能提高流水线的性能加 速比。 增强 ALU 功能 , 使其在与乘法器延时相差不大的情况 下,完成这些复合运算,将在保持主频不变的前提下,提高 声码器运算性能。在使用 TSMC 0.25 μm 工艺库进行测试性 综合后,得到乘法器的延时为 25 ns 左右,而 32 位加法器延 时为 10 ns, 因此本文设计了一种四级可重构的 ALU 单元: 首尾两级为规格化级,中间两级为计算级;计算级完成延时 较长的操作,如加、减、绝对值、取反运算等;而规格化级 完成延时较短的操作,如算术移位、求指数、比特运算等; 由指令译码器对各级的数据来源进行可重构的选通控制。 78 种复杂度不等的复合算术逻辑运算均可由该 ALU 单元在 单周期内完成。

表 1 部分常见复合运算操作

| 运算形式                                                                                      | 每 s 使用次数 | 运算功能                    |

|-------------------------------------------------------------------------------------------|----------|-------------------------|

| round((la< <b+lc)<<d)< td=""><td>24 000</td><td>32 位算术左移做 32 位加法左移并四舍五入</td></b+lc)<<d)<> | 24 000   | 32 位算术左移做 32 位加法左移并四舍五入 |

| round(la< <b)< td=""><td>120 000</td><td>32 位算术左移后四舍五入</td></b)<>                         | 120 000  | 32 位算术左移后四舍五入           |

| abs(la>>c)                                                                                | 24 000   | 32 位算术右移后求绝对值           |

| abs(la>>c)-lb                                                                             | 24 000   | 32 位算术右移后求绝对值, 再32 位减法  |

| (la+lb)>>c                                                                                | 40 000   | 32 位加法,算术右移             |

| round(la< <norm_l(lb))< td=""><td>1 600</td><td>32 位归一化后并四舍五入</td></norm_l(lb))<>         | 1 600    | 32 位归一化后并四舍五入           |

| a-b< <c< td=""><td>40 000</td><td>16 位算术左移作为减数进行 16 位减法</td></c<>                         | 40 000   | 16 位算术左移作为减数进行 16 位减法   |

乘法单元可单周期完成包括 32 位乘法等复合运算在内的 9 种 32/16 位定点乘法运算。乘累加操作是任何语音算法中都经常使用的,因此设计一个独立的乘累加单元以充分提高运行效率。6 个运算单元部件可同时并行工作。

(3)寄存器堆:整个寄存器堆分成 2 组,每组有 19 个 32 位通用寄存器单元,每个单元由 2 组 16 位寄存器拼接而成;每组各有 1 个读端口和 1 个写端口,整个寄存器堆可同时对 2 个 32 位寄存器进行读写操作,因此,单指令周期内可以完成 64 位、32 位或 16 位数据的存取。同时,为有效实现语音算法中多重嵌套过程调用,该寄存器堆采用重叠寄存器窗口的设计方法<sup>[4]</sup>,将 2 组寄存器堆各分成 3 层寄存器子堆,层与层之间有 2 个窗口寄存器共同可见,作为寄存器子堆之间信息交互的窗口,可以在嵌套过程调用时进行参数传递。

(4)数据通路部件:由6个独立的32位数据通路单元组

成,每个单元又分为高 16 位与低 16 位,因此,可同时进行 6 路 32 位或 12 路 16 位的数据传输或数据交换。这些数据通路单元由各运算部件、各存储器和寄存器堆等功能部件进行 共享,其数据可以送往各个功能单元,由指令译码部件来控制 6 个数据通路单元的数据来源和流向,并以重组的方式将各功能单元与各数据通路单元之间形成部件互联的可重构。

(5)双指令集:在针对语音编解码算法的专用处理器设计中,VLIW设计方法是非常适用的。VLIW体系结构能在复杂度较低的控制逻辑水平上产生较高的指令并行性<sup>[5]</sup>,从而使芯片在低主频下就能够实现语音编解码算法,这一点是优于通用DSP的。

采用可变长 VLIW 指令集,由基本指令集和专用指令集构成,基本指令集可以满足语音算法的实现需要,但是效率低,专用指令集可以最大限度地实现指令级并行性,提高算法实现的并行度。基本指令集的指令字长是 16 bit 的整数倍,最大 64 bit;专用指令集的指令字长是 64 bit 的整数倍,最大 256 bit。其中专用指令集的确定过程如下所述:分析语音算法中最耗费运算资源的程序部分,比如多重嵌套循环,将其按照软件流水的方式循环展开,并进行串并行分析,在满流水的情况下将所有可并行的存取、运算操作等提取成一条专用指令,使之能在满流水的情况下在单周期内完成一次循环操作,充分达到指令级并行。

#### 6 结束语

语音编解码算法、可重构技术的发展以及 VLIW 体系结构在专用微处理器领域的应用,为高并行度、低成本的语音编解码芯片的设计与应用创造了良好的机遇。本文设计的低速率可重构声码器能很好地满足数字保密通信等领域对高性能和高灵活性的应用需求。该声码器目前已完成原型设计,但还存在许多问题,仍需不断完善。

### 参考文献

- [1] Byun K J, Hahn M, Kim K S. Implementation of 13 Kb/s QCELP Vocoder ASIC[C]//Proc. of the 1st IEEE Asia-Pacific Conference on ASICs. Piscataway, NJ, USA: IEEE Press, 1999: 258-261.

- [2] 贾志科, 崔慧娟, 唐 昆, 等. 低速率语音编解码专用芯片的设计[J]. 清华大学学报, 1999, 39(5): 73-76.

- [3] 张建伟, 贺天宏, 李军林, 等. 高质量 0.6 Kb/s 声码器算法[J]. 清华大学学报, 2003, 43(4): 449-452.

- [4] 郭桂香. UltraSPARC 与 Itanium 寄存器机制的比较[J]. 高性能计 算技术, 2003, 30(1): 57-60.

- [5] 王 沁. VLIW 体系结构微处理器设计考虑[J]. 微计算机信息, 1999, 15(5): 6-7.

# (上接第234页)

控、连续的媒体流,为 VoD 服务提供了 QoS 保证。当然, CircleSearch 还需要进一步完善,进一步研究如何获得更好的 快捷节点,同时考虑稀有流行度的因素,研究适合于流行度 小的文件新的技术。

# 参考文献

- [1] Cohen B. Bittorrent Introdution[EB/OL]. (2003-05-01). http://bittorrent.com/introduction.html.

- [2] Guo Yang, Suh K, Kurose J, et al. P2Cast: P2P Patching Scheme for VoD Service[C]//Proc. of the WWW 2003. New York, USA: ACM Press, 2003: 301-309.

- [3] Guo Yang, Suh K, Kurose J, et al. A Peer-to-peer On-demand Streaming Service and Its Performance Evaluation[C]//Proc. of the IEEE ICME 2003. Maryland, USA: IEEE Press, 2003; 649-652.

- [4] Watts D J, Dodds P S, Newman M E J. Identity and Search in Social Networks[J]. Science, 2002, 296(5571): 1302-1305.