February 2007

工程应用技术与实现。

文章编号: 1000-3428(2007)04-0230-03

文献标识码: A

中图分类号: TN913

# 5Gbps~40Gbps 宽带交换软核的设计与实现

李宥谋,蒋林,韩俊刚

(西安邮电学院专用集成电路设计中心, 西安 710061)

摘 要:研究了 5Gbps~40Gbps 交换技术和 IP 软核的实现方法。采用多层结构、模块化的设计思想,使用 Verilog 硬件描述语言对 40Gbps 宽带交换电路进行编程,实现了一种通用的、容量可变的、可移植的宽带交换电路的 IP 软核,可以将其应用到 SDH 设备中的数字交叉连接电路中。

关键词:IP 软核;同步数字系列;T-S-T 交换;功能验证

# Design and Implementation of 5Gbps ~40Gbps Broad Band Switch Soft-core

LI Youmou, JIANG Lin, HAN Jungang

(ASIC Center, Xi'an University of Post and Telecommunications, Xi'an 710061)

[Abstract] This paper researches the implementation methods of the 5Gbps~40Gbps switch technology and IP soft-core. With the design idea of multilayer and modularization, it programs the 40Gbps broad band switch circuit in Verilog HDL. It realizes a versatile, alterable capability, transplantable IP Soft-core of the broad band switch circuit. The IP core can be used in the DXC circuits of the SDH equipment.

[Key words] IP soft-core; Synchronous digital hierarchy(SDH); T-S-T switch; Function verification

40Gbps宽带交换IP软核是基于 40Gbps宽带交换芯片基础之上,经过多次功能仿真和时序模拟实验而设计的一种通用IP软核。数据的接收和发送端口采用 16 位的并行155.52Mbps的速率,收发端口可以从 2 路扩展到 16 路,具有256×256 的STM-1/AU-4 无阻塞电路交换能力。如果采用多片结构或将空分交换模块容量扩容,则可支持更大容量的交换能力。在设计 40Gbps宽带交换IP软核的过程中,IP软核的验证、性能测试占了较大的工作量[1],设计分为总体设计、模块设计、模块级功能仿真、软核级功能仿真、软核级时序模拟、软核在FPGA上的性能测试共 6 个阶段。

# 1 40Gbps 宽带交换的简介

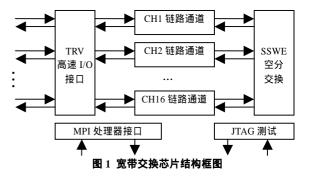

宽带交换芯片由数模混合电路组成,模拟部分提供 16路支持 PCML 电平接口标准、工作于 2.488Gb/s 的输入输出接口,数字部分完成解帧/成帧及交换功能。通过一个 16位的微处理器接口实现外部控制器对芯片的配置和工作状态的读取,采用 T-S-T 三级结构完成交换功能,其中空分交换是各链路通道之间的交换,与各链路通道独立。芯片内部有 16个独立的链路通道(CH1~CH16)模块,分别完成各个链路的解帧/成帧、发送/接收,接收端时隙交换、发送端时隙交换、指针解释和伪随机序列监测等功能,这 16 个模块功能是完全相同的,芯片电路设计规模较大、逻辑功能复杂,按照测试要求设计了一个 JATG 模块测试电路,宽带交换结构框图如图 1 所示。

(1)TRV 高速 I/O 接口:提供 16 路高速模拟差分信号的接收和发送,恢复时钟和数据。接收端口将收到的串行数据变换为并行数据送出,发送端口将送来的并行数据变换为串行数据。该模块采用数字和模拟混合设计方法。

(2)MPI 处理器接口模块:提供 16 位的微处理器接口,

实现对芯片内部寄存器的访问,还可完成中断请求信号的产生和处理、寄存器地址的第一级译码、根据地址总线高 8 位选通相应模块等功能。

(3)SSWE 空分交换模块:处于接收时隙交换和发送时隙交换之间,完成 16 条链路在空间上的数据交换功能,实现 STM-1(155.5Mbps)粒度上的交换,并支持 STM-1 粒度的多播和广播功能。

(4)CH 链路通道模块:共有 16 个模块,1 个模块对应 1 条链路。每个模块由 SDH 链路解帧子模块、接收端时分交换子模块、SDH 链路成帧子模块和指针解释与伪随机二进制序列(PRBS)监视子模块组成。

(5)JTAG 测试模块:支持 IEEE 1149.1 标准,提供部分端口的边界扫描、CH 链路的环回测试等功能。

**基金项目:**国家"863"计划基金资助项目(2003AA1Z1190);陕西省科研发展资助项目(2004K05-G4)

作者简介: 李宥谋(1959 - ), 男, 副教授, 主研方向: 网络通信, 集

成电路研究;蒋 林、韩俊刚,博士、教授

**收稿日期:**2006-03-01 **E-mail:**lym@xiyou.edu.cn

# 2 宽带交换 IP 核设计

知识产权(Intellectual property, IP),在电子电路设计中,IP核(IP Core)就是由第三方设计好的电路功能模块,可以直接用于专用集成电路(ASIC)、可编程器件(PLD)等电路设计,尤其以 FPGA 器件作载体的电路设计中。从实现形式和应用层次上来看,IP 核有 3 种不同形式:软核(Soft-Core),固核(Firm-Core)和硬核(Hard-Core)。

软核以可综合的硬件描述语言(HDL)描述的形式提交, 其性能通过时序模拟进行验证;硬核以集成电路版图掩模图 案的形式提交,经过实际工艺流片验证;处于软核和硬核之 间的固核以电路网表的形式提交,并通常采用硬件进行验证。

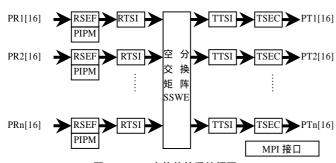

在 40Gbps 的宽带交换电路中,TRV 高速 I/O 接口部分,接收和发送要达到 2.488 Gbps 速率的性能,对电路的各项要求都非常严格,只有采用 IP 硬核设计,才能保证 2.488 Gbps 收发器的性能。但 IP 硬核设计的特点是版图固定,生产适应性差,难以应用推广。而根据 FPGA 器件发展的趋势分析,软核是可综合的程序代码,用户设计的自由度很大。嵌入高速收发器的 FPGA 器件越来越多,因此在设计宽带交换 IP 核时 不需要包含 TRV 高速 I/O 接口部分。图 2 给出了 5Gbps~40Gbps 交换 IP 软核的系统框图。

图 2 40Gbps 交换软核系统框图

40 Gbps 交换软核由 7 个不同的模块组成,其中 RSEF、PIPM、RTSI、TTSI 和 TSEC 5 个模块是各条链路重复使用的模块。PR 是 16 位并行接收数据,PT 是 16 位并行发送数据,下标 n 可以选择  $2\sim16$  条链路,各个模块的功能简介如下:

(1)RSEF: SDH链路解帧模块,主要实现帧定位功能,并 检测字符及帧定位的丢失;BIP-8 检查,提供B1 字节校验功 能;根据配置确定是否实现解扰码功能和输入数据的按位取 反功能。(2)RTSI:接收级时分交换模块,通过先进先出缓冲 器(FIFO)实现接收链路时钟与核心时钟的同步桥接;接收链 路帧位置与公共帧位置的同步,其中FIFO为 16 位宽 138 字 深;同步之后的数据可实现接收级时隙交换,或透明传输。 (3)TTSI:发送级时分交换模块,通过FIFO完成本链路发送时 钟与核心时钟的同步桥接。其中, FIFO为 16 位宽 4 字深; 接收前级模块的数据,完成发送级时隙交换,或透明传输。 (4)TSEC: SDH链路成帧模块,主要功能: A1/A2字节插入, JO 字节插入 ,B1 字节的计算及插入 ,伪随机序列产生及插入 , 插入错误B1 字节,单次插入错误A1/A2 字节,连续插入错误 A1/A2 字节,对发送数据扰码以及输出差分信号预加重控制 等功能。(5)PIPM:指针解释和PRBS监视模块,包含一个简 化的指针解释器,该解释器指示输入链路上SONET/SDH数据 净荷中的J1 字节位置以及后续的指针调整情况。它还可以监 测输入链路上级联的STM-16/VC4-16c净荷中的PRBS数据。 监测的PRBS数据按照 $X^{23} + X^{18} + 1$ 多项式生成。(6)MPI:微 处理器接口模块,提供本芯片与通用16位微处理器总线连接

接口,有 16 位地址线,地址空间可达 64KB,能产生中断请求信号和内部复位信号;实现对芯片内部各个寄存器的读写操作和各种中断源的控制。(7)SSWE:空分交换模块,有 15 种交换能力选择,从 5GB到 40GB不同容量均可选择。SSWE模块由交叉矩阵和连接控制存储器组成。连接控制存储器由两个页面组成:其中一个页面称为主用(active),控制当前交换,用户不能修改;另一个页面称为备用(standby),可由用户修改,确定修改完成后,将工作在active的页面切换成standby页面,同时将修改后的standby页面切换成active页面,实现对交换链路的修改。

电路的工作过程:RSEF 模块从收发器接收 16 位并行数据,进行 SDH 帧定位,B1 字节校验和数据解扰码,随后送到 RTSI 模块的 FIFO 缓冲器中,进行链路的帧同步并与核心时钟域的同步桥接,之后进行接收级时分交换;然后送入空分交换矩阵,将数据交换到所要求的目的链路,再进行发送级时分交换,实现要求输出的时隙顺序;最后经 SDH 成帧后送给发送器。

# 3 关键性的技术

在 5Gbps~40Gbps 宽带交换 IP 核的设计过程中,申请了4项发明专利,其关键性的技术表现在以下几个方面。

# 3.1 STM-16 的帧定位算法

SDH帧结构<sup>[2]</sup>采用以字节为单位的矩形块状,由 9 行 270 列组成,每列可以有N B,用STM - N表示;其中N表示容量的大小。传输一帧的时间为 125us,即帧频为 8kHz。对应STM-16,N = 16,它的一帧有 9(行)×270(列)×16(字节) = 38 880 B;传输速率 38 880×8 000×8(bit) = 2 488 320 000bit/s。

第 1 行开始的 3 列为 A1 , 紧随其后的 3 列是 A2 ; A1 和 A2 是帧定位字节(帧同步字)。A1 为 11110110 , A2 为 00101000 , 用于识别帧的起始位置。在速率为 2.488 Gbps 的 STM-16 帧结构中 , 帧定位有  $3\times16=48$  个 A1 字节和  $3\times16=48$  个 A2 字节。

在数据传输中,由于数据编码有可能和同步字的编码相同,因此需要根据 SDH 的帧结构来确认是否为帧同步字,如果确认是同步字,状态才能进入帧同步,否则继续寻找帧同步字。在进入了同步状态后,在规定的位置检测不到帧同步字,就会发生帧丢失现象,出现了帧失步。在确认帧同步字的过程中,由于传输中数据受到的损伤、干扰,会产生误码,或者是接收器的串并转换定位不对,都可使帧同步字识别出现错误。因此按照什么规则来识别帧的位置,将影响帧定位的正确性、速度以及电路实现的复杂程度。

综合各种因素,将帧定位过程分为 4 个阶段,用状态转移图实现。4 个状态为帧失步状态、帧定位状态、帧同步状态、帧丢失状态,状态之间转移按照规定的算法进行。经过仿真和模拟实验,各项指标符合 SDH 的相关协议规定,而且达到了电路简单、识别正确率高、帧定位速度快目的。

# 3.2 T-S-T3 级交换

电路交换是实现 5Gbps~40Gbps宽带交换的核心,要求交换的粒度为STM-1/AU-4,交换单位为字节;达到 256×256 无阻塞交换,并且支持多播和广播功能。实现的方法可以有许多种,但是采用不同的交换模式,所需的硬件资源和对资源的速度要求差别很大。常用的交换模式有单级T型、单级S型、多级T型、多级S型、多级混合型S-T-S和T-S-T<sup>[3]</sup>等交换电路,经过比较和分析认为时分-空分-时分(T-S-T)3 级交换结构是最佳方案,可以充分利用FPGA器件上资源。

接收级和发送级的时分交换由存放交换数据的数据存储器、控制时隙交换的控制存储器和 FIFO 电路组成。控制存储器由主用和备用两套组成。主用控制存储器控制时隙交换,用户不能修改;如果需要修改交换的控制参数,用户只能通过修改备用控制存储器,然后将备用转入主用,实现对时隙交换控制参数的修改。接收级时分交换的控制方式采用顺序写入、控制读出的操作。而发送级时分交换电路,采用控制写入、顺序读出的操作方式。两种电路相比,只是数据存储器的写入和读出的控制方式不同,电路的其它部分相似。

S 级空分交换主要由交叉点矩阵和连接控制存储器组成,实现了多个输入复用链路与多个输出复用链路之间的空间交换,这种交换不改变时隙位置。交叉点矩阵由数据选择器组成开关矩阵,空分的一次交换可实现两个时隙在空间上的同时交换。每条链路有 16 个时隙,形成 16 个时隙空分交换面,经过 8 次的空分交换时间就可以完成。连接控制存储器保存 16 个时隙空分交换面的控制信息,每一条链路对应两个多路选择器,多路选择器根据选择容量的大小确定,共有15 种选择器,从 2 选 1 , 3 选 1 , ... , 16 选 1。

# 3.3 链路之间的同步

在 5Gbps~40Gbps 宽带交换 IP 软核中,用户可以按 STM-16 粒度选择不同的容量。在空分交换模块中,各条输入链路时隙必须同步,而在高速的数据传输电路中,不同链路之间很难采用同一个时钟。因此将传送的数据编码成自同步的数据流发送。在每条链路的接收端由时钟数据恢复(CDR)电路实现时钟和数据的分离,将恢复的时钟分频和数据进行串并转换后送给软核中的 RSEF 模块,通过 RTSI 模块中的FIFO 缓冲器实现与软核提供的核心时钟和帧同步时钟桥接,达到所有链路数据帧结构序列完全同步。

同一个设备中的链路之间的不同步,主要由背板之间、器件的连线之间和器件内部信号处理时的不同延时所产生,估算链路之间的最大延时就可以确定 FIFO 缓冲器的深度。软核的核心时钟和帧同步时钟由设备系统的时钟源提供。软核中帧同步时钟的帧头定位有两种方式:(1)通过软核中的配置寄存器指定帧头的位置;(2)由软核内部电路按照指定的算法自动计算帧头的位置。

除此之外,还有 SDH 指针解释、内建自测试、链路标记的装入与检测等功能,在该软核设计中都得到了很好的解决。

# 4 结束语

随着IT业的发展,深亚微米工艺的提高、集成电路中的 MOS管尺寸进一步缩小,使得流片费用和设计难度随之增大<sup>[4]</sup>。因此采用嵌入专用硬核的FPGA器件,实现各种专用电路将是一种较好的选择。在国家"十五"科技攻关项目 (2002BA106B)"40Gbps专用交换芯片"设计中,采用FPGA器件做载体,使用了40Gbps宽带交换IP软核,实现了40Gbps专用交换芯片的所有功能,达到了项目规定的要求,为我们积累了丰富的经验。在国家"863计划"项目(2003AA1Z1190)"160Gbps数据交叉连接芯片"的设计中,对40Gbps宽带交换IP软核做部分的修改,即可直接移入到该项目中,大大减轻了设计工作量,并取得了良好的效果。

## 参考文献

- 1 李宥谋, 韩俊刚. SDH 芯片功能验证平台的设计与实现[J]. 光通信研究, 2005, (4): 61-63.

- 2 孙学康, 毛京丽. SDH 技术[M]. 北京: 人民邮电出版社, 2004.

- 3 桂海源. 程控交换与宽带交换[M]. 北京: 中国人民大学出版社, 2000.

- 4 韩俊刚. 论 ASIC 与 FPGA 之争[J]. 计算机工程, 2004, 30(8): 10-12.

(上接第 229 页)

根据上述方程组可以得到系数矩阵以及常数向量,调用方程组求解算法得到其中一个解向量为[0101]。由该例可以看出,对于采用不同扫描结构的电路,计算种子的过程完全相同。唯一的区别是在构造线性方程组时,系数矩阵会有所不同。本节提出的种子求解算法适用于采用其它任何扫描结构的电路。

#### 5 实验结果

对于 ISCAS89 基准电路实现了扫描森林的 BIST 结构 , 并针对其中部分较大的电路做了大量的实验。本文的算法是 在 SUN Blade 2000 上编制运行的。表 1 给出了实验结果。

表 1 提出的方案与 seed-per-pattern 方案实验结果比较

| Circuit  | LFSR | Bit     | Seed per Pattern |        | Proposed Scheme |        | D . 1(0/) |

|----------|------|---------|------------------|--------|-----------------|--------|-----------|

|          | Size | Counter | # seeds          | # bits | # seeds         | # bits | Red(%)    |

| s9234    | 81   | 12      | 66               | 5 346  | 17              | 1 965  | 63.2      |

| s9234.1  | 81   | 12      | 90               | 7 290  | 36              | 3 566  | 51.1      |

| s13207   | 45   | 10      | 156              | 7 020  | 47              | 3 205  | 54.3      |

| s13207.1 | 100  | 13      | 10               | 1 300  | 1               | 2 17   | 83.3      |

| s38584   | 72   | 9       | 88               | 6 336  | 34              | 2 934  | 53.7      |

| s38584.1 | 97   | 15      | 33               | 3 201  | 8               | 1 151  | 64.0      |

将本文提出的方法与传统的一码一种(Seed per Pattern) 方法进行了对照实验。第 3 列给出了实现提出方法需要的二 进制计数器的位数。第 4~7 列给出了两种方法的种子数以及 数据存储位数。第8列给出了数据存储位数降低的比率。

实现本文提出的重播种方案需要一个二进制计数器来进行移位操作。由于在基于扫描的 BIST 结构中,其本身需要一个二进制计数器来控制扫描移位操作,因此通常并不需要额外的硬件开销。以基准电路 s13207 为例,s13207 共有触发器 669 个,若采用单链完全扫描结构,需要一个 10 位二进制计数器,与本文提出方案所需的计数器相同。

#### 参考文献

- 1 Koenemann B. LFSR-coded Test Patterns for Scan Designs[C]//Proc. of European Test Conf.. 1991: 237-242.

- 2 Xiang D, Gu S, Sun J G, et al. A Cost-effective Scan Architecture for Scan Testing with Non-scan Test Power and Test Application Cost[C]//Proc. of ACM/IEEE Design Automation Conference. 2003: 744-747.

- 3 Xiang D, Li K W, Fujiwara H. Design for Cost-effective Scan Testing by Reconstructing Scan Flip-flops[C]//Proc. of the 14<sup>th</sup> IEEE Asian Test Symposium. 2005.

- 4 Alyamani A A, Mitra S, Mccluskey E J. Optimized Reseeding by Seed Ordering and Encoding[J]. IEEE Trans. on Computer-aided Design of ICAS, 2005, 24(2): 264-270.

- 5 Rajski J, Tamarapalli N, Tyszer J. Automated Synthes Is of Phase Shifters for Built-in Self-test Applications[J]. IEEE Trans. on Computer-aided Design of ICAS, 2000, 19(10).